Устройство управления и синхронизации - Электрическая структурная схема микропроцессорной системы

Базовым интервалом времени, на котором основана синхронизация работы всего микроконтроллера, является машинный цикл. Машинный цикл имеет фиксированную длительность и содержит 6 состояний S1-S6, каждое из которых по длительности соответствует такту, и, в свою очередь, состоит из двух временных интервалов определяемых фазами P1 и P2. Таким образом, каждый машинный цикл состоит из 12 периодов входного тактового сигнала и при частоте последнего 12 Мгц составляет 1 мкс. Дважды за один машинный цикл формируется сигнал ALE.

Входной тактовый сигнал вырабатывается либо встроенным тактовым генератором микроконтроллера при подключении к его выводам X1 и X2 кварцевого резонатора (см. Рис. 5 а) или LC-цепочки (см. Рис. 5 б), либо внешним источником тактовых сигналов (см. Рис. 5 в).

а

В случае LC-цепочки частота опорного синхросигнала определяется выражением

В случае внешнего тактового генератора его выход подключается ко входу X1, а вывод X2 подключается к общей шине.

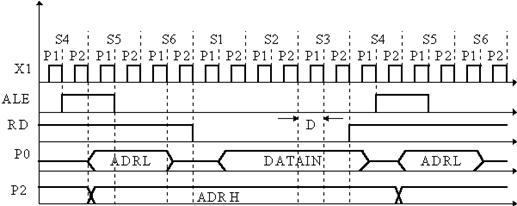

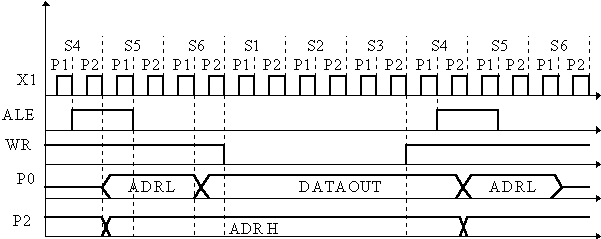

Внешний интерфейс микроконтроллера предназначен для организации взаимодействия его с внешней памятью программ и данных и устройствами ввода-вывода. Обмен данными осуществляется по внешней мультиплексной магистрали микроконтроллера. Эта магистраль использует выводы порта P0 для выдачи младшего байта адреса и чтения/записи байта данных, а выводы порта P2 - для выдачи старшего байта адреса. Обращение к внешней памяти данных требует двух машинных циклов. Поэтому второй импульс ALE внутри машинного цикла при обращении к внешней памяти данных не генерируется.

Рисунок 6. Цикл чтения из внешней памяти данных

По срезу сигнала ALE младший байт адреса, поступающий с выводов порта P0, должен быть зафиксирован во внешнем регистре-защелке. Старший байт адреса держится на выводах порта P2 в течение всего цикла и не требует внешней фиксации. Данные считываются в фазе P1 состояния S3 текущего машинного цикла. К этому моменту они должны быть заведомо установлены на шине данных.

Рисунок 7. Цикл записи во внешнюю память данных

При обращении к внутренней памяти данных сигналы RD и WR не вырабатываются. Однако сигнал ALE вырабатывается всегда.

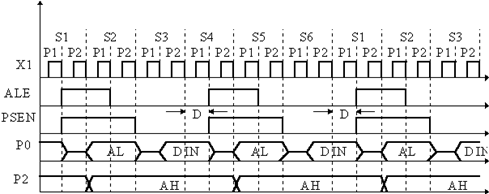

Для обращения к внешней памяти программ используется механизм отличный от механизма обращения к памяти данных. Для фиксации слов программы используется специальный сигнал PSEN. При этом сигналы ALE и PSEN вырабатываются дважды за машинный цикл. Если второй выбираемый байт в команде не используется, то он игнорируется. При переходе к выполнению следующей команды он будет считан вторично.

Рисунок 8. Цикл чтения внешней памяти программ

Так же, как и в случае памяти данных, младший байт адреса должен быть зафиксирован во внешнем регистре по срезу сигнала ALE. Байты программы считываются в фазе P1 состояний S4 и S1 текущего машинного цикла. При обращении к внутренней памяти программ сигнал PSEN не генерируется.

Работа с внешней памятью программ разрешена лишь при низком уровне на входе EA. При этом микроконтроллер считает, что вся память программ расположена во внешней памяти. При высоком уровне сигнала на этом входе микроконтроллер реализует цикл обращения к внешней памяти программ лишь в случае, если требуемый адрес выходит за пределы внутреннего сегмента памяти программ. Если в микросхеме "прошит" бит секретности, то уровень сигнала на входе EA фиксируется при сбросе микроконтроллера во внутренней защелке и дальнейшее его изменение не влияет на работу системы.

Начальная установка (аппаратный сброс) производится с целью запуска или перезапуска микроконтроллера после подачи на него напряжения питания. Сброс осуществляется подачей на вход RESET высокого уровня и удержания его в течение не менее двух машинных циклов. Этот сигнал может подаваться асинхронно по отношению к внутреннему тактированию. Вход RESET постоянно опрашивается микроконтроллером в момент S5P2 каждого машинного цикла. После сигнала сброса порты ввода-вывода находятся в неизменном состоянии в течение 19-ти периодов тактирования, после чего в промежутке между 19-м и 31-м тактом переводятся в начальное "единичное" состояние. При этом сигналы ALE и PSEN находятся в неактивном (высоком) состоянии. По сигналу сброса микроконтроллер устанавливает все служебные регистры в начальное состояние. На содержимое внутренней памяти данных сигнал RESET не влияет. При включении питания она устанавливается в произвольное состояние. Длительность сигнала RESET должна быть не меньше времени необходимого для запуска внутреннего генератора плюс 2 машинных цикла. В свою очередь время установки генератора зависит от частоты синхронизации и характеристик кварцевого резонатора. При частоте 10 Мгц оно обычно составляет около 1 мкс.

Для автоматического рестарта микросхемы после подачи напряжения питания, к выводу RESET необходимо подключить RC-цепочку (см. рис. 9), обеспечивающую требуемую задержку, позволяющую генерировать одиночный импульс сброса.

После снятия сигнала RESET проходит от 1 до 2 тактовых периодов до их активизации. При этом микроконтроллер начинает выполнять программу с адреса 0000h внутренней либо внешней памяти программ (в зависимости от уровня сигнала EA).

Удержание выводов ALE и PSEN в активном (нулевом) состоянии при активном сигнале RESET приводит к переводу всех выводов микросхемы в высокоимпедансное состояние (режим "ONCE"). Этот режим используется для отладки системы.

Похожие статьи

-

Резидентная память - Электрическая структурная схема микропроцессорной системы

Память программ и память данных, размещенные на кристалле ОМК физически и логически разделены, имеют различные механизмы адресации, работают под...

-

Программная модель ОМК - Электрическая структурная схема микропроцессорной системы

ОМК выполняет действия над 8-разрядными операндами. Программная модель CPU MCS-51 содержит шесть регистров. Все регистры, кроме счетчика команд PC,...

-

Система команд - Электрическая структурная схема микропроцессорной системы

Система команд МК51 содержит 111 базовых команд, которые удобно разделить по функциональному признаку на пять групп: - команды передачи данных; -...

-

Где Г - генератор; ССУ - схема синхронизации и управления; УР - управление режимом; СС и У - сигналы синхронизации и управления; МП - микропроцессор;...

-

Общая часть - Электрическая структурная схема микропроцессорной системы

Intel 8051 (К1816 ВЕ51) имеет в своем составе следующие аппаратурные средства. - 8-разрядный процессор MCS-51 (в его состав входят 1 - байтное АЛУ и...

-

Составление структурной схемы Конвейерная линия на установки "Cannon Viking Maxfoam" представляет собой ограниченное по краям пространство, вследствие...

-

При линеаризации коэффициент при текущем напряжении определяется как производная от напряжения управления. Подставляя сюда установившееся значение...

-

Введение - Электрическая структурная схема микропроцессорной системы

Характерная черта научно-технического прогресса, определяющего дальнейший мощный подъем общественно-технического производства: широкое внедрение...

-

Проектируемая система адаптивного управления представляет собой комплексную систему автоматического регулирования, состоящую из двух подсистем,...

-

Хотя габаритные размеры всех трех холодильников почти одинаковые, однако сильно отличается объем холодильной камеры и морозильного отделения. Таблица...

-

Типы соединений Существуют различные типы входов и выходов. Один может получать сигналы с датчиков и выключателей, другой - получать сигнал напряжения,...

-

Для управления установкой нами запроектирован микропроцессорный контроллер АК2 - РС301А, производства компании "Danfoss" (Дания). Общие сведения Основное...

-

ТАЛЕВАЯ СИСТЕМА, НАЗНАЧЕНИЕ, СХЕМЫ И УСТРОЙСТВО - Буровое оборудование

НАЗНАЧЕНИЕ, СХЕМЫ И УСТРОЙСТВО В процессе проводки скважины подъемная система выполняет различные операции. В одном случае она служит для проведения СПО...

-

Рис. 3.3. Схема замещения фазы асинхронного двигателя Полное сопротивление разветвления: Z R '( S ) = R R '( S ) + j* X R '( S ). Полное сопротивление...

-

В качестве электрической схемы рассмотрим пускатель бесконтактный нереверсивного типа ПБН-160 предназначен для обеспечения плавного нарастания напряжения...

-

Структурная схема предлагаемого дискретного анализатора частотного спектра сигнала, представленного в [7] как устройство для вычисления модулей...

-

Структурная схема После обоснования выбора структурной схемы устройства останавливаемся на схеме с одним дешифратором. Структурная схема приведена на...

-

Описание задачи проектирования Данная система предназначена для установки "Cannon Viking Maxfoam", которая в свою очередь предназначена для производства...

-

СКС состоит из ББК, трансформатора СОБС-2М, устанавли-ваемых в шкафу УЗП и четырех датчиков КЗК, устанавливаемых на фундаментах УЗ. Датчики КЗК соединены...

-

Устройства заградительный Устройства заграждения в количестве 4-х изделий: из которых 2-правых и 2-левых; правые УЗ устанавливаются в правую сторону...

-

Исходные данные Исходными данными для проектирования статического преобразователя электрической энергии являются параметры применяемого асинхронного...

-

Запуск системы производства поролона производится по команде оператора после того, как им были введены параметры протекания процесса. Перед запуском...

-

Настройка контроллера и управление контроллером осуществляются через персональный или карманный компьютер при помощи программы "AK2-Service Tool"....

-

Функциональная схема системы На основании исходных дифференциальных уравнений функциональную схему системы отработки заданного напряжения можно...

-

Обоснование способа описания исходной АСР Для того чтобы проанализировать данную систему необходимо составить ее математическую модель. Каждый элемент...

-

Разработка структурно-функциональной схемы стенда управления шаговым двигателем Постановка задачи Предметом изучения и объектом управления был выбран...

-

Разработка структурной схемы системы защиты информации с использованием анализатора частотного спектра сигнала Предлагаемый способ защиты и увеличения...

-

Расчет прогнозной интенсивности отказов электрической схемы БСКЛ Эксплуатационная интенсивность отказов резисторов постоянного сопротивления ЛЭRпост =...

-

Питание электродвигателей приводов Устройств заграждения осуществляется от однофазной сети переменного тока. Для питания электроприводов от однофазной...

-

На рисунке 2.7 представлена принципиальная схема системы электропривода, а также на рисунке 2.8 его структурная схема. Рисунок 2.7- Принципиальная схема...

-

Переходную характеристику по задающему воздействию строят на основании ее передаточной функции Данная характеристика представлена на рисунке 1.12...

-

Активное сопротивление обмотки статора Для четырехполюсной машины с неизолированными лобовыми частями: K 1=1,25; B =1 мм. Зубцовое деление, отнесенное к...

-

В инженерной практике принято промышленные холодильные камеры описывать линейным дифференциальным уравнением 1-го порядка с постоянными коэффициентами....

-

Датчик Скорости MD-256 изображенный на рисунке 4.4 предназначен для работы с конвейерами. Рисунок 4.4 - Датчик Скорости MD-256 Он передает сигнал на...

-

Выбираю преобразователь КТЭ 320/220 А (440 В) Семейство продуктов КТЭ Тип изделия или компонента Привод с регулируемой частотой вращения Специальное...

-

Системы автоматического регулирования, контроля и управления

Функциональные схемы систем автоматического регулирования, контроля и управления Под управлением понимают такую организацию процесса, которая...

-

Холодильная автоматизированная установка состоит из трех компрессоров (КМ), оснащенных устройствами автоматической защиты, маслоотделителя (МО), сборника...

-

Принцип работы системы и функциональная схема САР В данной работе рассматривается система автоматического регулир Ования температуры воды в баке. Схема...

-

Расчет тока уставки группы №1. Установлена мощность ламп P1 = 8*100 =800 Вт. Рабочий ток I1 равняется: I1 = P1 / U = 800/ 220 =3,64 A Принимаем ток...

-

Изучение частотных характеристик типовых динамических звеньев систем автоматического управления

ЛАБОРАТОРНАЯ РАБОТА ИССЛЕДОВАНИЕ ЧАСТОТНЫХ ХАРАКТЕРИСТИК ТИПОВЫХ ДИНАМИЧЕСКИХ ЗВЕНЬЕВ САУ Передаточный автоматический система частотный Целью настоящей...

Устройство управления и синхронизации - Электрическая структурная схема микропроцессорной системы