Этап логического проектирования - Разработка цифрового комбинационного устройства демультиплексора

Исходная логическая схема устройства

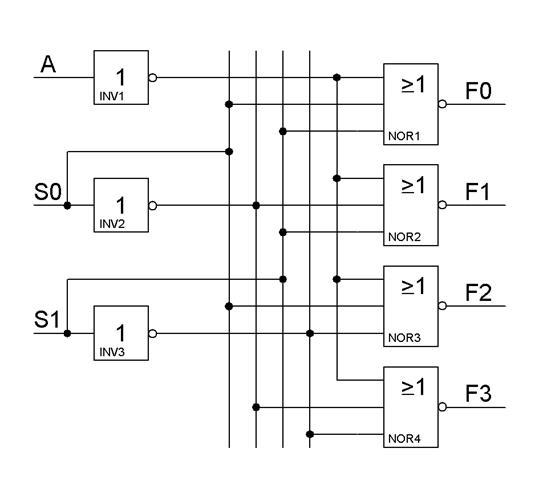

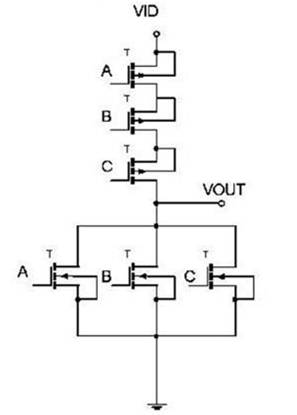

Исходная логическая схема устройства для данной логической функции показана на рисунке 3.1. Для разработки и создания устройства нам необходимо и достаточно использовать только два типа логических элементов - инвертор и 3ИЛИ-НЕ. Необходимости преобразовывать данную логическую схему нет.

Рисунок 3.1. Исходная логическая схема устройства

Результаты логического моделирования спроектированного устройства

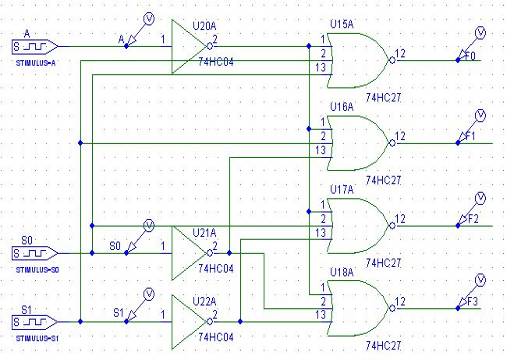

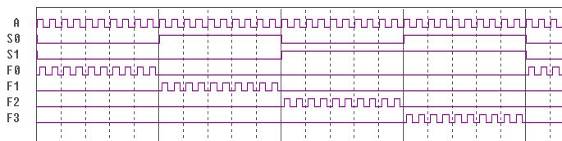

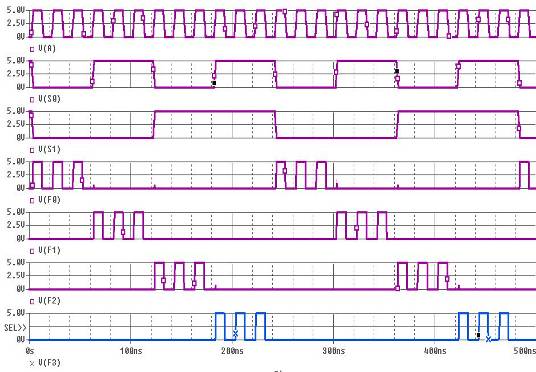

На рисунках 3.2 и 3.3 представлены соответственно созданная логическая схема устройства и результаты логического моделирования спроектированного устройства, удовлетворяющего заданию на курсовой проект.

Рис. 3.2. Логическая схема устройства

Рис. 3.3. Результаты логического моделирования устройства

IV. Этап схемотехнического проектирования

Электрические схемы используемых логических элементов в КМДП-базисе

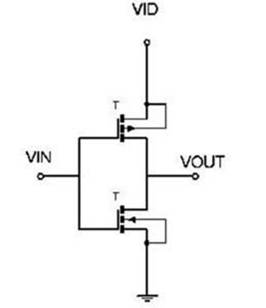

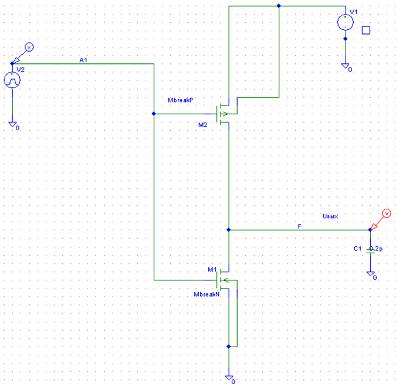

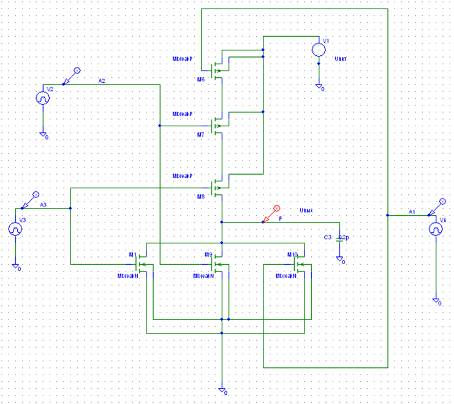

На рисунках 4.1 и 4.2 показаны электрические схемы инвертора и элемента 3ИЛИ-НЕ, на рисунках 4.3 и 4.4 - их схемы при расчете в программе Schematics.

Рис. 4.1. Электрическая схема инвертора

Рис. 4.2. Электрическая схема элемента 3ИЛИ-НЕ

Рис. 4.3. Инвертор

Рис. 4.4. 3ИЛИ-НЕ

Предварительный расчет параметров транзисторов

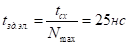

- 1. 2. Находим период тактового сигнала при рабочей частоте fT, максимально допустимое время задержки на схеме в целом tСХ и допустимое время задержки на каждый логический элемент tЗД ЭЛ:

, ,

Транзистор мультиплексор сигнал тактовый

3. Выбираем размеры транзисторов в эквивалентном инверторе, обеспечивающем время задержки не хуже tЗД ЭЛ:

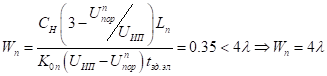

Полагая, что, получим

Учитывая вышеприведенные расчеты, мы получили для логических элементов следующие параметры:

Инвертор

, ,

3ИЛИ-НЕ

, ,

Результаты расчета переходных процессов в логических элементах в программе Schematics

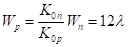

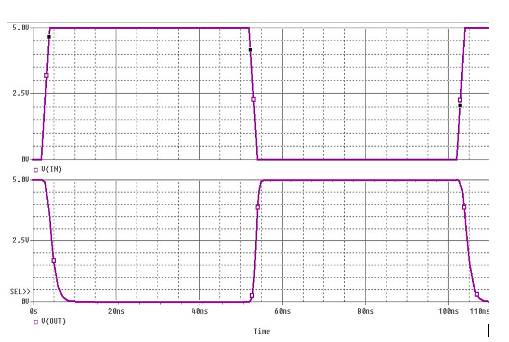

На рисунках 4.5 и 4.6 представлены результаты расчетов переходных процессов в логических элементах, используемых при создании демультиплексора, в программе Schematics. Все расчеты удовлетворяют условиям, поставленным в задании на курсовой проект.

Рис. 4.5. Результаты расчетов переходных процессов в инверторе

, , ,

Рис. 4.6. Результаты расчета переходных процессов в элементе 3ИЛИ-НЕ

, , ,

Расчет переходного процесса устройства в целом в программе Schematics

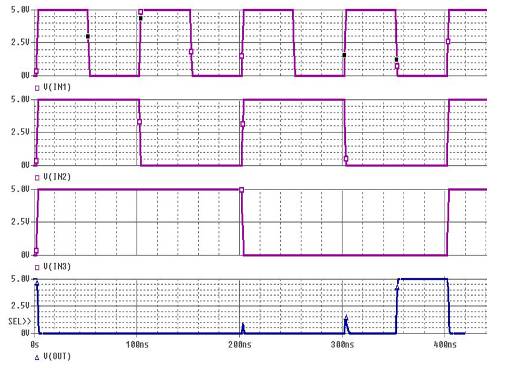

На рисунке 4.7 представлен результат расчета переходных процессов для всего устройства в целом программе Schematics.

Рис. 4.7. Результат расчета переходных процессов всего устройства

Для данного демультиплексора получены следующие характеристики:

, , ,

V. Этап топологического проектирования

Топология логических элементов

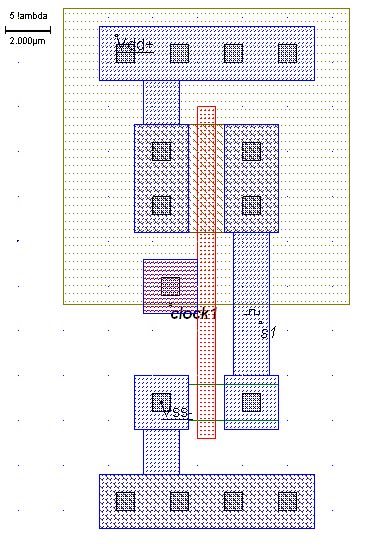

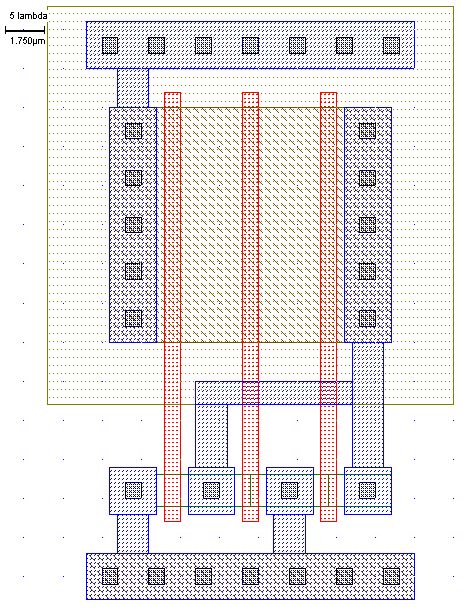

Топология логических элементов Инвертор и 3ИЛИ-НЕ представлены соответственно на рисунках 5.1 и 5.2.

Рис. 5.1. Топология инвертора

Рис. 5.2. Топология элемента 3ИЛИ-НЕ

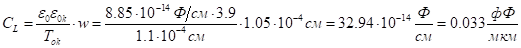

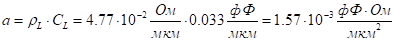

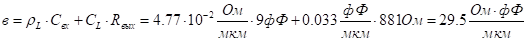

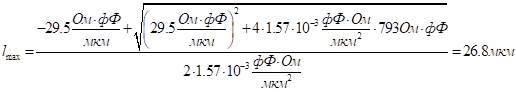

Расчет максимальной длины межсоединений

Будем считать, что влиянием межсоединений можно пренебречь, если при учете паразитных емкостей и сопротивлений, связанных с разводкой, изменение постоянной времени в цепи составляет не более 5%. В этом случае для однозвенной RC-цепочки можно получить аналитическую оценку максимальной допустимой длины межсоединений, не вносящих существенных искажений в переходной процесс.

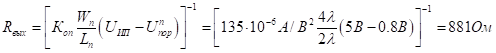

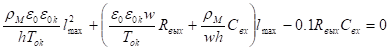

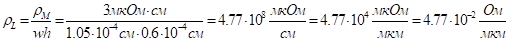

Ограничение на длину межсоединений должно быть получено из условия:

М/0=1.05

Отсюда

- (RВЫХ1+ RМ)(СМ +СВХ2)/ (RВЫХ1СВХ2) = 1.05; (RВЫХ1+ М lM/(wMhM)) (е0 еOKlMwM / TOK +СВХ2)/(RВЫХ1СВХ2) = 1.05;

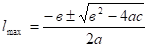

И максимальное значение lM может быть найдено как решение квадратного уравнения

(М е0 еOK / (hMTOK ))lM2 + (RВЫХ1е0 еOKwM / TOK + СВХ2М /(wMhM))lM - - 0.05RВЫХ1 СВХ2 = 0;

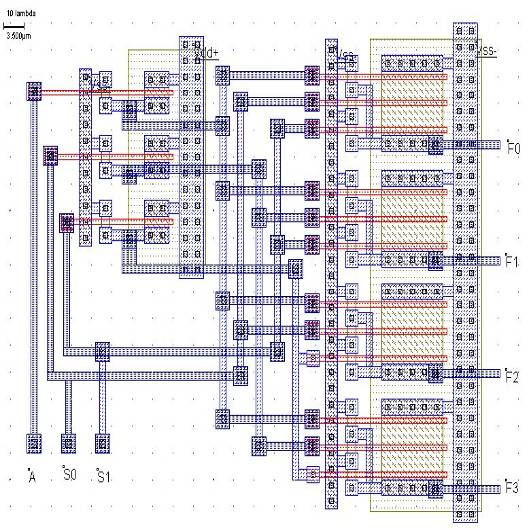

Эскиз топологии устройства

Эскиз топологии всего устройства показан ниже на рисунке 5.3.

Рис. 5.3. Эскиз топологии устройства

Расчет паразитных сопротивлений и емкостей разводки

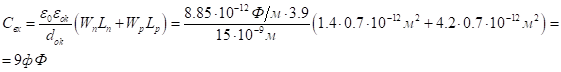

Значение емкости оценим по формуле

,

Где

Толщина межслойной изоляции, ,

Площадь обкладок паразитного конденсатора. Площадь обкладок для емкости металл - подложка рассчитывается как площадь участка металлической шины, соединяющего два или несколько электрических узлов с учетом разветвлений.

- -абсолютная диэлектрическая проницаемость диэлектрика, =, - относительная диэлектрическая проницаемость диэлектрика, .

Что составляет меньше от значения. Следовательно, в дальнейшем мы влияние паразитной емкости учитывать не будем

Похожие статьи

-

Вариант № 6 Необходимо разработать цифровое комбинационное устройство демультиплексор из 1 в 4 в базисе ИЛИ-НЕ, НЕ, логическая функция которого указана...

-

Выводы по работе - Разработка цифрового комбинационного устройства демультиплексора

При разработке демультиплексора, удовлетворяющего заданию на курсовой проект, мы получили следующие характеристики используемых логических элементов и...

-

Устройство сравнения предназначено для определения знака входного сигнала, а также для сравнения сигнала с УВХ с сигналом, снимаемым с ЦАП, и выдачи...

-

Помимо аналого-цифровых преобразователей (АЦП), работой цифровой логики могут управлять операционные усилители (ОУ) и компараторы, преобразующие...

-

Применяя к выражению (13) аксиому двойного отрицания (9) получим: Yмажор =~(~( x2*x0 + x1*x0 + x2*x1))(14) Формуле (14) соответствует схема (рис.8,слева)...

-

МИНИМИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ, ТАБЛИЦА КАРНО - Цифровые устройства и микропроцессоры

Полученные по формуле СДНФ (12) выражение может быть преобразовано (не всегда) к виду, имеющему меньшее число переменных и операций по сравнению с...

-

Частота генератора тактовых импульсов, Гц....190 Счет ведется от числа....9 Шаг...............................1 Число состояний системы............8...

-

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПАМЯТЬ) - Цифровые устройства и микропроцессоры

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и...

-

Расчет схемы электрической принципиальной цифрового матрицирующего устройства. Рассмотрим систему обозначений сигналов, принятую в цифровом телевидении...

-

СПОСОБЫ ПРЕДСТАВЛЕНИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ - Цифровые устройства и микропроцессоры

Целью проектирования цифрового устройства является получение его логической функции (ЛФ) и соответствующей ей схемной реализации. ЛФ могут иметь...

-

КОМБИНАЦИОННЫЕ СХЕМЫ, ДЕШИФРАТОР - Цифровые устройства и микропроцессоры

В комбинационных схемах логическая функция зависит только от комбинации значений входных переменных. При описании многих цифровых устройств невозможно...

-

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти...

-

Для n-логических переменных (аргументов) существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции...

-

Современный процесс разработки технического устройства можно разбить на следующие составные части: Научно-исследовательская работа (НИР);...

-

ЛОГИЧЕСКИЙ БАЗИС, СХЕМНЫЕ ОСОБЕННОСТИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ - Цифровые устройства и микропроцессоры

Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Функции И, ИЛИ, НЕ не являются минимальным ЛБ, т....

-

Для сетей доступа разработаны оптические волновые коммутаторы и маршрутизаторы. Основой этих устройств являются волновые конверторы: л-конверторы,...

-

"Введение, этапы развития электроники" - Электроника и схемотехника аналоговых устройств

Электроника-область науки, техники и производства, охватывающая изучение физических основ, исследование, разработку и принципы использования приборов,...

-

Заключение - Разработка радиопередающего устройства

Главной задачей данного курсового проекта было спроектировать РПУ, которое позволяет передавать цифровую информацию (код) с помощью частотной...

-

При помощи программы моделирования электрических цепей Fastmean). Программы моделирования электрических цепей (такие как OrCAD PSPICE, Micro-Cap,...

-

Расчет и проектирование пассажирских устройств Для обслуживания пассажиров и нужд самой станции в проекте предусматривается: - пассажирское здание; -...

-

На промежуточных станциях для выполнения грузовых операций сооружаются крытый склад общего пользования, крытая и открытая платформа, контейнерная и...

-

Анализ характеристик объекта проектирования трудовой деятельности человека, производственной среды Фотоприемное устройство является модулем приемной...

-

Проектирование УВХ. - Разработка аналого-цифрового преобразователя

При обработке аналоговых сигналов, изменяющихся с частотой, соизмеримой или большей, чем скорость работы АЦП, из аналогового сигнала приходится делать...

-

Структурная схема разрабатываемого устройства представлена на рисунке 3.1. Рисунок 3.1. Структурная схема устройства. 1 - Входной буферный каскад 2 -...

-

Цифровые устройства и микропроцессоры

Введение Счетчики выполняют на запоминающих элементах - триггерах. Он фиксирует число импульсов, поступивших на его вход. В интервалах между ними счетчик...

-

Разработка функциональной схемы устройства - Разработка автомобильной охранной сигнализации

Функциональная схема автомобильной сигнализации показана на рисунке 6. Функциональная схема брелока управляющего автомобильной сигнализацией показана на...

-

Расчет электрической емкости представляет весьма сложную физико-математическую задачу. В инженерной практике используются справочные данные, готовые...

-

Термином оптимальный синтез определяют процесс построения устройства с заданными свойствами, оптимально учитывающий совокупность технико-экономических...

-

Рассчитываем элементы схемы автогенератора, Расчет ГУНа - Разработка радиопередающего устройства

Для улучшения стабильности частоты целесообразно выбрать контур с высокой добротностью (Qнен - добротность ненагруженного контура ) и большим...

-

Описание блок-схемы программы (рис. 3.1). Блок № 1 - начало программы. В этом блоке происходит инициализация всей программы, создание основного и...

-

Построение эпюр силовых факторов Для начала подбора сечений необходимо определить расчетные схемы стабилизатора и оси и нагрузки, действующие на них....

-

Выбор конструктивно-силовой схемы агрегата Представляется несколько вариантов регулярной конструктивно-силовой схемы (КСС) агрегата: нервюрно-стрингерный...

-

Цель: вычислить потребляемую мощность схемы программатора. Данные по элементам и рассчитанная мощность сведены в таблицу 2. Таблица 2 - Потребляемая...

-

Введение - Проектирование фильтров нижних частот

Лестничный реактивный фильтр нижняя частота В современных системах связи широко применяются электрические фильтры: LC-фильтры, активные RC - фильтры,...

-

ОСНОВНЫЕ ПОЛОЖЕНИЯ АЛГЕБРЫ ЛОГИКИ В отличие от аналоговых электронных устройств, в цифровых устройствах (ЦУ) входные и выходные сигналы могут принимать...

-

Конструкция -- совокупность деталей, узлов и материалов с разными физическими свойствами, находящимися между собой в определенной физической связи...

-

В данной дипломной работе был спроектирован алгоритм расчета и программа, позволяющая рассчитывать некоторые характеристики нерегулярных...

-

ПУ усиливает электрический сигнал, обеспечивая наибольшее отношение сигнал/шум. Основные требования, предъявляемые к ПУ - минимальные шумы, максимальный...

-

Кроме вышеперечисленных искажений в аналоговой ВОСПИ возможно возникновение искажений сигнала в ФПУ при использовании в качестве фотодиодов лавинных...

-

Комплекс устройств локомотивного хозяйства Устройства локомотивного хозяйства располагаются на тяговой территории, занимающей место на территории...

Этап логического проектирования - Разработка цифрового комбинационного устройства демультиплексора