ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

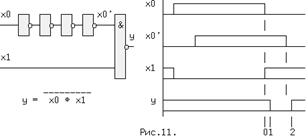

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти помехи имеют вид коротких импульсов, и в некоторых случаях приводят к серьезным сбоям в работе схем. Рассмотрим устройство на рис.11. Если элементы схемы не вносят задержки сигнала, а x0 и x1 находятся в противофазе, т. е. x0 = ~x1, то y = ~(x1 * ~x1) = 1. Если же каждый из пяти ЛЭ имеет задержку tзд. р., тогда x0' запаздывает относительно x0 на 4tзд. р. и на выходе схемы возникает незапланированный "отрицательный" импульс (интервал 1..2), сдвинутый на tзд. р. элемента И-НЕ (интервал 0..1). Процесс прохождения входных сигналов до общего выхода называется состязаниями или "гонками".

Вредный эффект "гонок" может быть устранен несколькими способами, один из которых заключается

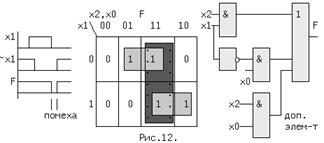

В добавлении к ЛФ дополнительного слагаемого. Пусть некоторая ЛФ равна F = x1*x2 + ~x1*x0, тогда при x2=x0=1 может появиться помеха, вызванная тем, что сигнал ~x1 задержан относительно x1 на величину задержки инвертора (см. рис.12).

Добавление лишнего импликанта (в таблице обведен точками) устраняет проблему, т. к.при критической ситуации, когда x2=x0=1, дополнительная составляющая x0*x2=1 и функция F = x1*x2 + ~x1*x0 + x0*x2 равна всегда 1 при x2=x0=1.

В устройствах индикации такие короткие помехи можно игнорировать, так как они будут незаметны для глаз.

Похожие статьи

-

Применяя к выражению (13) аксиому двойного отрицания (9) получим: Yмажор =~(~( x2*x0 + x1*x0 + x2*x1))(14) Формуле (14) соответствует схема (рис.8,слева)...

-

Помимо аналого-цифровых преобразователей (АЦП), работой цифровой логики могут управлять операционные усилители (ОУ) и компараторы, преобразующие...

-

ПРОГРАММИРУЕМЫЕ ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ - Цифровые устройства и микропроцессоры

Проектирование современных цифровых устройств невозможно без использования программируемых цифровых ИС (ПЦИС). Они обладают следующими преимуществами...

-

ЛОГИЧЕСКИЙ БАЗИС, СХЕМНЫЕ ОСОБЕННОСТИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ - Цифровые устройства и микропроцессоры

Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Функции И, ИЛИ, НЕ не являются минимальным ЛБ, т....

-

ТРИСТАБИЛЬНЫЕ ЭЛЕМЕНТЫ - Цифровые устройства и микропроцессоры

Наряду с двумя логическими состояниями существует третье технологическое состояние, когда выход элемента отключается от внутренней схемы. При этом...

-

РЕВЕРСИВНЫЙ СЧЕТЧИК - Цифровые устройства и микропроцессоры

Схема двухразрядного счетчика с общим входом сброса R, выходом переноса CR при суммировании и выходом переноса BR при вычитании приведена на рис. внизу....

-

D - ТРИГГЕР СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ - Цифровые устройства и микропроцессоры

D - триггер имеет два входа: информационный вход D(аtа) и вход управления записью/запоминанием (защелкиванием) L(oad)/L(atch) - отсюда его второе имя :...

-

Расчет схемы электрической принципиальной цифрового матрицирующего устройства. Рассмотрим систему обозначений сигналов, принятую в цифровом телевидении...

-

Для n-логических переменных (аргументов) существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции...

-

T - ТРИГГЕР, ВЗАИМНЫЕ ПРЕОБРАЗОВАНИЯ ТРИГГЕРОВ - Цифровые устройства и микропроцессоры

Анализ временной диаграммы при J = K = 1 (рис. 46) позволяет сделать два важных вывода. Во-первых, период повторения выходных импульсов увеличился в два...

-

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПАМЯТЬ) - Цифровые устройства и микропроцессоры

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и...

-

ПРИМЕНЕНИЕ СЧЕТЧИКОВ В ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ - Цифровые устройства и микропроцессоры

На рисунке внизу последовательно включены 6 счетчиков с модулем 10 (двоично - десятичные). Информационные выходы Qi каждого каскада через преобразователь...

-

МУЛЬТИПЛЕКСОР - Цифровые устройства и микропроцессоры

Мультиплексор передает сигнал с одного из информационных входов xi на единственный выход y, причем номер этого входа равен десятичному эквиваленту...

-

СХЕМА СРАВНЕНИЯ КОДОВ - Цифровые устройства и микропроцессоры

Два кода X и Y считаются равными, если попарно равны их одноименные разряды. Можно ввести функцию F(X==Y), которая равна 1, если xi=yi для всех i, иначе...

-

КОМБИНАЦИОННЫЕ СХЕМЫ, ДЕШИФРАТОР - Цифровые устройства и микропроцессоры

В комбинационных схемах логическая функция зависит только от комбинации значений входных переменных. При описании многих цифровых устройств невозможно...

-

СИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Если незадействованные входы элементов И-НЕ 1 и 2 соединить вместе (рис. 36), получится синхронный RS - триггер со статическим управлением...

-

АСИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Асинхронный триггер имеет два входа S(et) - установка и R(eset) - сброс и два выхода прямой - Q и инверсный - ~Q. Триггер переходит из текущего состояния...

-

Устройство передающее сигнал с информационного входа на один из выходов, причем номер этого выхода равен десятичному эквиваленту двоичного кода на...

-

ОПРЕДЕЛЕНИЯ НЕКОТОРЫХ ПАРАМЕТРОВ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ - Цифровые устройства и микропроцессоры

Ниже приведены некоторые параметры в отечественном по ГОСТ 19480-89 и международном обозначении. Tзд. р.1,0 / tPHL - время задержки распространения при...

-

СЧЕТЧИКИ - Цифровые устройства и микропроцессоры

Счетчик (Сч) - последовательностная схема, преобразующая поступающие на вход импульсы в код Q, пропорциональный их количеству. Большинство счетчиков...

-

В таблице приведены усредненные типовые значениянекоторых параметров микросхем, выполненных по различным технологиям. В различных справочникахприведенные...

-

РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА - Цифровые устройства и микропроцессоры

Название указывает, что сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую. Одна из возможных схем трехразрядного...

-

Микросхемы РПЗУ допускают многократное, до сотен тысяч, циклов перепрограммирования на рабочем месте пользователя. Это свойство обеспечивается...

-

ОЗУ СТАТИЧЕСКОГО ТИПА - Цифровые устройства и микропроцессоры

В качестве элемента памяти используется простейший D-триггер защелка. В микросхеме 537РУ10 каждая ЯП состоит из восьми триггеров и располагаются ячейки...

-

РЕГИСТРЫ, ПАРАЛЛЕЛЬНЫЕ И ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ - Цифровые устройства и микропроцессоры

Последовательностныесхемысразличнымикомбинациямипоследовательногои параллельного способов записи и считывания информации. Выполняются на основе...

-

АЦП ПАРАЛЛЕЛЬНОГО ТИПА - Цифровые устройства и микропроцессоры

В таком АЦП весь диапазон входного напряжения разбивается на 2^n интервалов. Каждому интервалу соответствует опорное напряжение Uо(i), снимаемое с...

-

СУММАТОРЫ - Цифровые устройства и микропроцессоры

Сумматор осуществляет арифметическое суммирование n-разрядных кодов X=(x(n-1),..,x0) и Y=(y(n- 1),..,y0). Правила сложения двух одноразрядных двоичных...

-

КАСКАДНОЕ ВКЛЮЧЕНИЕ СЧЕТЧИКОВ, СЧЕТЧИК - ТАЙМЕР - Цифровые устройства и микропроцессоры

Рассмотрим последовательное включение n - счетчиков с различными модулями счета Mi. Возможна постановка двух задач. В первой необходимо определить...

-

Логический элемент И-НЕ с открытым коллектором (ОК) (см. рис.2. слева) обозначается в поле элемента ромбом с чертой внизу. К открытому коллектору снаружи...

-

АСИНХРОННЫЙ СЧЕТЧИК C ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В качестве примера возьмем четырехразрядный счетчик. Четыре двоичных разряда счетчика обеспечивают М = 16 состояний. Ниже приведена схема и условное...

-

Цифровые устройства и микропроцессоры

Введение Счетчики выполняют на запоминающих элементах - триггерах. Он фиксирует число импульсов, поступивших на его вход. В интервалах между ними счетчик...

-

СХЕМА КОНТРОЛЯ ЧЕТНОСТИ (НЕЧЕТНОСТИ) - Цифровые устройства и микропроцессоры

Схема применяется для выявления одиночных ошибок, вызванных помехами в линии связи или в блоках памяти. Метод основан на подсчете числа единиц в...

-

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ СХЕМЫ, ТРИГГЕРЫ - Цифровые устройства и микропроцессоры

В последовательностных схемах (ПС) выходные сигналы зависят не только от комбинаций входных, но и от значений самих выходных сигналов в предшествующий...

-

МИНИМИЗАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ, ТАБЛИЦА КАРНО - Цифровые устройства и микропроцессоры

Полученные по формуле СДНФ (12) выражение может быть преобразовано (не всегда) к виду, имеющему меньшее число переменных и операций по сравнению с...

-

Программируемыепостоянныезапоминающиеустройства(ППЗУ)делятсянаоднократно программируемые (например, биполярные ПЗУ с плавкими соединениями) и...

-

ШИФРАТОР - Цифровые устройства и микропроцессоры

Шифратор (Ш) может быть неприоритетным, если допускается подача только одного активного сигнала и может быть приоритетным, если допускается подача...

-

СИНХРОННЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В синхронном счетчике импульсы поступают на тактовые входы всех триггеров одновременно. Ниже на рисунке ниже приведен трехразрядный счетчик с модулем...

-

Этап логического проектирования - Разработка цифрового комбинационного устройства демультиплексора

Исходная логическая схема устройства Исходная логическая схема устройства для данной логической функции показана на рисунке 3.1. Для разработки и...

-

СПОСОБЫ ПРЕДСТАВЛЕНИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ - Цифровые устройства и микропроцессоры

Целью проектирования цифрового устройства является получение его логической функции (ЛФ) и соответствующей ей схемной реализации. ЛФ могут иметь...

-

Схема ДТЛ - диодно-транзисторной логики - Электроника и схемотехника аналоговых устройств

Основная схема ДТЛ приведена на рисунке 2.16,а. Здесь диоды VD1, VD2, VD3 и резистор R1 представляют собой конъюнктор (И), элементы VT, R2, R3 _ инвертор...

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры