Архітектура пам'яті процесора ADSP-BF534 - Розробка процесора ШПФ

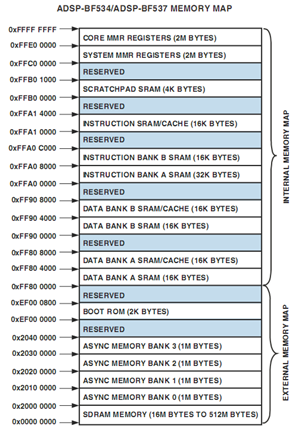

Процесор ADSP-BF534 розглядає пам'ять як один уніфікований 4 GB адресний простір, використовуючи 32-розрядну адресацію. Всі ресурси, в тому числі вбудована пам'ять, зовнішня пам'ять і регістри контролю вводу/виводу, займають окремі розділи цього спільного адресного простору. Частини пам'яті цього адресного простору розташовані у вигляді ієрархічної структури, щоб забезпечити добрий баланс між ціною і продуктивністю з деякою дуже швидкою, кеш пам'яттю на кристалі чи SRAM і більш об'ємною й дешевшою й повільнішою зовнішньою пам'яттю. Пам'ять на кристалі має найвищу швидкодію доступну для процесора Blackfin. Системи зовнішньої пам'яті доступні через зовнішній модуль шинного інтерфейсу, який надає змогу підключити SDRAM, флеш пам'ять і SRAM при необхідності доступу до 516 Мб фізичної пам'яті. DMA контролер пам'яті забезпечує високу широкосмугову пропускну здатність. Він може здійснювати передачу блоків коду чи даних між внутрішньою пам'яттю і зовнішніми просторами памяті.

Зовнішня пам'ять доступна через EBIU. Це 16-ти розрядний інтерфейс, що забезпечує безпосереднє підключення до банку синхронної DRAM (SDRAM), а також до чотирьох банків асинхронних пристроїв пам'яті, включаючи Flash, EPROM, ROM, SRAM і адресовані пам'яттю пристрої вводу/виводу.

Рис. 1.3 Карта адресації пам'яті процесора ADSP-BF534

РС133 SDRAM сумісний контролер може бути запрограмований для двохсторонньої взаємодії з 128М SDRAM. Окремий рядок може бути відкритий для кожного SDRAM внутрішнього банку і SDRAM контролер підтримує до 4 внутрішніх банків SDRAM, задля підвищення загальної швидкодії. Асинхронний контролер пам'яті може бути запрограмований на управління чотирма банками пристроїв з дуже гнучкими часовими параметрами для широкого кола пристроїв. Кожний банк займає 1Мб незалежно від розміру використовуваних пристроїв, отже ці банки є суміжними кожний із яких може бути окремо заповненим.

Похожие статьи

-

Опис ядра процесора ADSP-BF534 - Розробка процесора ШПФ

Ядро процесора ADSP-BF534 складається із двох 16-бітних помножувачів, двох 40-бітних акумуляторів, двох 40-бітних АЛП, чотирьох відео АЛП і з 40-бітного...

-

Повністю схема функціональна подана у додатку. Нижче розписано основні аспекти стосовно розробки кожного окремого вузла. Розробка вузла синхронізації...

-

Як вказано було вище, не будемо вдаватися в дискусію щодо того, яка з архітектур краще - CISCчи RISC, Гарвардська чи Прінстонська. Розглянемо відмінності...

-

6 Застосування дискретного перетворення Фур'є - Розробка процесора ШПФ

1. Цифровий спектральний аналіз - Аналізатори спектра - Обробка мови - Обробка зображень - Розпізнавання образів 2. Проектування фільтрів - Обчислення...

-

Підключення вхідного інтерфейсу PPI, Підключення зовнішньої ПЗП типу EEPROM - Розробка процесора ШПФ

Programmable Peripheral Interface - двонаправлений напівдуплексний програмований інтерфейс периферійних пристроїв - використовують для зв'язку з...

-

2 Опис процесора ADSP-BF534 - Розробка процесора ШПФ

Процесор ADSP-BF534 являє собою процесор сімейства Blackfin з розширеними можливостями, тобто володіє більшою продуктивністю і меншою споживаною...

-

1 Розрахунок часу виконання - Розробка процесора ШПФ

Для розрахунку часу виконання алгоритму ШПФ на процесорі ADSP-BF525 потрібно визначити кількість операцій додавання, множення та читання/запису з/до...

-

Аналіз блок-схеми виконання ШПФ - Розробка процесора ШПФ

На рис.2.1 представлено обчислення ШПФ з використанням алгоритму з прорідженням за частотою з кількістю точок 1024. Цей метод потребує, щоб алгоритм...

-

Швидке перетворення Фур'є - Розробка процесора ШПФ

Вихідними даними для ШПФ є елементи обмеженої послідовності x(n), де n=0,1,.. N-1. Відповідно дискретне перетворення Фур'є має вид: (1) (2) Де -...

-

Нижче наведена граф-схема алгоритму роботи програми. Рис. 5.1 Граф-схема алгоритму роботи програми Висновки Під час виконання курсового проекту було...

-

Підключення вихідного інтерфейсу SPI - Розробка процесора ШПФ

SPI ( Serial Peripheral Interface, SPI bus -- послідовний периферійний інтерфейс, шина SPI ) -- послідовний синхронний стандарт передачі даних в режимі...

-

Характеристики процесора ADSP-BF534 - Розробка процесора ШПФ

Особливості: - Ядро ADSP-BF534 з частотою до 500 МГц; - Максимальна продуктивність, 1000 MMACS; - Три 16-розрядних помножувачі; - Два 40-розрядних АЛП; -...

-

Опис контактів процесора ADSP-BF534 - Розробка процесора ШПФ

Призначення контактів процесора ADSP-BF534 наведені в таблиці 1. З метою забезпечення максимальної функціональності та скорочення розміру корпусу і...

-

Архітектура контролерів серії C51 - Структурні особливості сучасних мікропроцесорних систем

В даний час серед усіх 8-розрядних мікроконтролерів - сімейство MCS-51 є безсумнівним чемпіоном з кількості різновидів і кількості компаній, що...

-

Архітектура PIC контролерів - Структурні особливості сучасних мікропроцесорних систем

PIC16fXX - це 8-розрядні FLASH CMOS мікроконтролери з RISC архітектурою, вироблені фірмою Microchip Technology. Це сімейство мікроконтролерів...

-

Перш ніж перейти до класифікації систем кондиціонування, слід зазначити, що загальноприйнятої класифікації до цих пір не існує, і пов'язано це з...

-

Розробка технічного завдання - Створення комутаційної техніки на основі цифрових систем передачі

Для даного мікрорайону потрібно впровадити цифрову систему комутації (ЦСК) типу Квант-Є. Для початку розрахунку проектованої мережі потрібно визначитись...

-

Основний недолік аналогових РРЛ є те, що викривлення переданих по них сигналів, які виникають у процесі формування, перетворення, ущільнення і...

-

Визначення коефіцієнтів технічної готовності і випуску Коефіцієнт технічної готовності б Т являє собою відношення кількості технічно справного рухомого...

-

Методи налагодження пристрою Пристрій не вимагає налагодження, тому що він налагоджується при виготовлені його на заводах, перед початком експлуатації...

-

Опис портів введення-виведення MS DOS може працювати з трьома паралельними пристроями (LPT1 - LPT3). Для підключення використовується стандартне...

-

Опис принципової схеми Пульт керування Пульт керування кондиціонером містить два РКІ індикатора поточної температури приміщення і задається користувачем...

-

Для обгунтування власного технічного рішення робимо висновки з інформації наведеної в пункті 8. 1. Наявність в кондиціонері такої базової функції, як...

-

Архітектура мікроконтролерів сімейства AVR - Структурні особливості сучасних мікропроцесорних систем

Мікроконтролери ATmega є 8-розрядними CMOS мікроконтролерами з AVR удосконаленою RISC архітектурою. Виконуючи більшість команд за один тактовий цикл,...

-

Призначення та напрямок застосування Пристрій, який проектує'ця - кондиціонер - призначений для введення бажаної температури в приміщенні, виведення...

-

Оскільки заданий мені передавач є стаціонарний то він буде працювати від мережі 220 В. Попередні каскади розраховані на живлення 12.6 В, а вихідний на 28...

-

Зазвичай в РЛС сантиметрового діапазону у якості малошумлячого підсилювача МШП надвисоких частот НВЧ використовують тільки напівпровідниковий...

-

Вимірювач частота сигнал потужність Пристрій повинен складатися зі зовнішнього пульта, який під'єднується до паралельного порта ПЕОМ. Пульт повинен мати...

-

Розробка функціональної схеми моноімпульсної РЛС Виходячи з послідовності операцій, які виконує моноімпульсни система, її функціональна схема повинна...

-

У варіантах реалізації приладу, розглянутих у 1 розділі немає можливості задавати частоту вихідного сигналу, а тільки амплітуду, що не задовольняє умови...

-

Рис.3 Блок-схема мікроконтроллеру ATtiny2313A/4313 ATtiny2313A/4313 - економічні 8-розрядні КМОП-мікроконтролери, виконані на основі покращеної...

-

Технологічний процес складання і контролю функціонування виробів PEA являє собою дуже складну систему, яка складається з множини функціональних одиниць і...

-

Вступ В приладах з радіо та електричними пристроями слабких струмів широко застосовується друкований монтаж - нанесення на поверхню основи, виготовленої...

-

Згідно технічного завданя необхідно розробити тракт ТА-А (АМ) й також ТА-Б (ПС). Функціональна схема з'єднувального тракту наведена в додатку Е. Умови...

-

Визначається кількість абонентських модулів на ОПС і ПС, що відповідає числу ГТ до УКС. На станції застосовуються два типи модулів: абонентський модуль...

-

Розробка варіантів реалізації функцій - Процес виготовлення друкованої плати

Для реалізації F1 запропоновані наступні варіанти: А) RC-генератор з Г-подібним контуром (А); В) генератор з мостом Віна (Б); Г) генератор з подвійним...

-

Пристрій виконаний за технологією поверхневого монтажу на друкованій платі із двостороннього скляного текстоліту розміром 200x135мм. Процес виготовлення...

-

Розробка структурної схеми МТМ На МТМ здійснюється впровадження цифрових систем комутації (ЦСК) методами "накладення" ЦСК на існуючу аналогову мережу і...

-

Тема роботи: Вивчення роботи регістрів. Мета роботи: Ознайомитись З Умовним графічним позначенням регістрів. Вивчити режими роботи регістру. Вивчити...

-

У лінію низького тиску входять фільтри грубого і тонкого очищення палива, паливоподаючий насос з додатковим насосом для ручного прокачування системи і...

Архітектура пам'яті процесора ADSP-BF534 - Розробка процесора ШПФ