Аналіз блок-схеми виконання ШПФ - Розробка процесора ШПФ

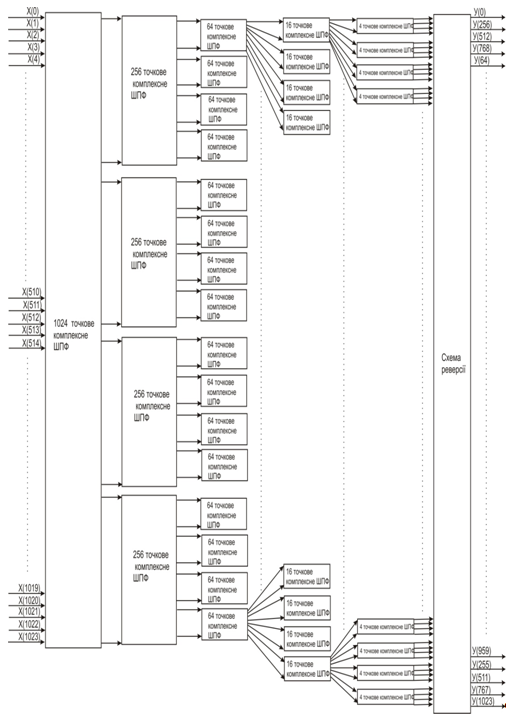

На рис.2.1 представлено обчислення ШПФ з використанням алгоритму з прорідженням за частотою з кількістю точок 1024. Цей метод потребує, щоб алгоритм реверсії був застосований до адресів вихідних відліків X(k).

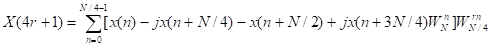

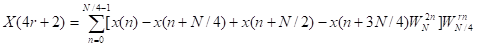

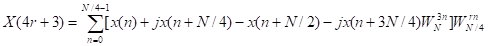

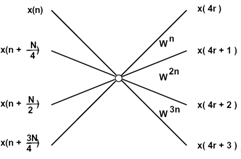

На першому етапі алгоритму рис.2.1 виконуються 16 чотирьох точкові ШПФ від елементів кожного стовпця. Потім проводяться повороти, причому показники експонент повертаючих множників вказані перед позначенням елементів пам'яті другого етапу. Потім всі чотири рядки проріджуються шляхом формування з них матриць розміром (44) і перетворяться по схемі 16-точкового ШПФ з основою 4, але з іншими повертаючими множниками. У табл. 2.2 наведені групи відліків, які беруть участь в базових операціях при виконанні алгоритму ШПФ при N=1024. ШПФ відбувається за 5 кроків згідно формули v = logRN (log41024), де r - основа ШПФ, а N - розрядність ШПФ. На виході відбувається четвіркова реверсія, згідно табл.2.1. Для кодування 1024-розрядного ШПФ необхідно 5 розрядів, тобто с4 с3С2С1С0 (с=0.1,2,3). Для переведення у десяткову систему числення необхідно виконати перетворення:

Таблиця.2.1 Четвіркова реверсія

|

Початкова послідовність |

Послідовність з реверсією | ||

|

Дес. с.числ. |

Четв. код |

Четв. код. |

Дес. с.числ. |

|

0 |

00000 |

00000 |

0 |

|

1 |

00001 |

10000 |

256 |

|

2 |

00002 |

20000 |

512 |

|

3 |

00003 |

30000 |

768 |

|

4 |

00010 |

01000 |

64 |

|

1021 |

33331 |

13333 |

511 |

|

1022 |

33332 |

23333 |

757 |

|

1023 |

33333 |

33333 |

1023 |

Таблиця 2.2. Групи відліків, які беруть участь в базових операціях

|

Номер базової операції |

Номер ітерації |

Інверсія | ||||

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

256 |

64 |

16 |

4 |

1 |

256 | |

|

512 |

128 |

32 |

8 |

2 |

512 | |

|

768 |

192 |

48 |

12 |

3 |

768 | |

|

2 |

1 |

256 |

64 |

16 |

4 |

64 |

|

257 |

320 |

80 |

20 |

5 |

320 | |

|

513 |

384 |

96 |

24 |

6 |

576 | |

|

769 |

448 |

112 |

28 |

7 |

832 | |

|

3 |

2 |

512 |

128 |

32 |

8 |

128 |

|

258 |

576 |

144 |

36 |

9 |

384 | |

|

514 |

640 |

160 |

40 |

10 |

640 | |

|

770 |

704 |

176 |

44 |

11 |

896 | |

|

4 |

3 |

768 |

192 |

48 |

12 |

192 |

|

259 |

832 |

208 |

52 |

13 |

448 | |

|

514 |

896 |

224 |

56 |

14 |

704 | |

|

771 |

960 |

240 |

60 |

15 |

960 | |

|

5 |

4 |

1 |

256 |

64 |

16 |

16 |

|

260 |

65 |

272 |

68 |

17 |

272 | |

|

515 |

129 |

288 |

72 |

18 |

528 | |

|

772 |

193 |

304 |

76 |

19 |

784 | |

|

253 |

252 |

63 |

783 |

963 |

1008 |

63 |

|

508 |

127 |

799 |

967 |

1009 |

319 | |

|

764 |

191 |

815 |

971 |

1010 |

575 | |

|

1020 |

255 |

831 |

975 |

1011 |

831 | |

|

254 |

253 |

319 |

847 |

979 |

1012 |

127 |

|

509 |

383 |

863 |

983 |

1013 |

383 | |

|

765 |

447 |

879 |

987 |

1014 |

639 | |

|

1021 |

511 |

895 |

991 |

1015 |

895 | |

|

255 |

254 |

575 |

911 |

995 |

1016 |

191 |

|

510 |

639 |

927 |

999 |

1017 |

447 | |

|

766 |

703 |

943 |

1003 |

1018 |

703 | |

|

1022 |

767 |

959 |

1007 |

1019 |

959 | |

|

256 |

255 |

831 |

975 |

1011 |

1020 |

255 |

|

511 |

895 |

991 |

1015 |

1021 |

511 | |

|

767 |

959 |

1007 |

1019 |

1022 |

767 | |

|

1023 |

1023 |

1023 |

1023 |

1023 |

1023 |

Рис. 2.1 Обчислення 1024-точкового ШПФ, алгоритм прорідження за частотою

3. Розрахунковий розділ

Похожие статьи

-

1 Розрахунок часу виконання - Розробка процесора ШПФ

Для розрахунку часу виконання алгоритму ШПФ на процесорі ADSP-BF525 потрібно визначити кількість операцій додавання, множення та читання/запису з/до...

-

Нижче наведена граф-схема алгоритму роботи програми. Рис. 5.1 Граф-схема алгоритму роботи програми Висновки Під час виконання курсового проекту було...

-

Швидке перетворення Фур'є - Розробка процесора ШПФ

Вихідними даними для ШПФ є елементи обмеженої послідовності x(n), де n=0,1,.. N-1. Відповідно дискретне перетворення Фур'є має вид: (1) (2) Де -...

-

Вихідні дані: адреси блоку - 160636, 160640; напруга живлення логічного блоку - 5В; напруга живлення зовнішніх пристроїв - 24 В; індикація станів схеми;...

-

Перш ніж перейти до класифікації систем кондиціонування, слід зазначити, що загальноприйнятої класифікації до цих пір не існує, і пов'язано це з...

-

Для шинних формувачів вибираємо 4 мікросхеми К589АП26. Вхідний вузол формуємо на мікросхемах КР1533ЛЕ1 - 4 незалежних елементи "2 ИЛИ-НЕ". Сигнал ВБ...

-

РРС Р-415 призначена для створення тимчасових швидкорозгортаємих малоканальних радіорелейних ліній зв'язку, а також для відгалуження каналів від...

-

Повністю схема функціональна подана у додатку. Нижче розписано основні аспекти стосовно розробки кожного окремого вузла. Розробка вузла синхронізації...

-

Робота блоку розпочинається з того, що центральний процесор формує на лініях КДА00-15Н адрес, він надходить на шинні формувачі (DD1-DD4), і при цьому...

-

За вихідними даними нам потрібно реалізувати: формувач сигналу, що реалізує функцію 4-х вхідних сигналів за ознакою більшості; формувач сигналів Fx та...

-

Опис ядра процесора ADSP-BF534 - Розробка процесора ШПФ

Ядро процесора ADSP-BF534 складається із двох 16-бітних помножувачів, двох 40-бітних акумуляторів, двох 40-бітних АЛП, чотирьох відео АЛП і з 40-бітного...

-

Робота блоку розпочинається з того, що центральний процесор формує на лініях КДА00-15Н адрес, він надходить на шинні формувачі (ШФ), і при цьому...

-

2 Опис процесора ADSP-BF534 - Розробка процесора ШПФ

Процесор ADSP-BF534 являє собою процесор сімейства Blackfin з розширеними можливостями, тобто володіє більшою продуктивністю і меншою споживаною...

-

Вступ - Розробка блоку зв'язку з електроавтоматикою верстата 16Б16. Пристрій управління шпінделем

Числове програмне керування (ЧПК) (англ. Computer numerical control) - комп'ютеризована система керування, яка зчитує командні інструкції спеціалізованої...

-

6 Застосування дискретного перетворення Фур'є - Розробка процесора ШПФ

1. Цифровий спектральний аналіз - Аналізатори спектра - Обробка мови - Обробка зображень - Розпізнавання образів 2. Проектування фільтрів - Обчислення...

-

Розроблений пристрій призначений для проведення лабораторної роботи з предмету "Цифрова схемотехніка". Він дозволяє дослідити та наочно показати роботу...

-

Архітектура пам'яті процесора ADSP-BF534 - Розробка процесора ШПФ

Процесор ADSP-BF534 розглядає пам'ять як один уніфікований 4 GB адресний простір, використовуючи 32-розрядну адресацію. Всі ресурси, в тому числі...

-

Підключення вихідного інтерфейсу SPI - Розробка процесора ШПФ

SPI ( Serial Peripheral Interface, SPI bus -- послідовний периферійний інтерфейс, шина SPI ) -- послідовний синхронний стандарт передачі даних в режимі...

-

Підключення вхідного інтерфейсу PPI, Підключення зовнішньої ПЗП типу EEPROM - Розробка процесора ШПФ

Programmable Peripheral Interface - двонаправлений напівдуплексний програмований інтерфейс периферійних пристроїв - використовують для зв'язку з...

-

У запропонованій курсовому проекті описана будова і принцип дії системи живлення автомобіля c5. Викладено також основи його експлуатації, технічного...

-

Щоб визначити загальну потужність, що споживається нашим блоком, потрібно спочатку визначити потужність, що споживають мікросхеми. Занесемо всі...

-

Призначення датчика тиску з цифровим блоком управління Датчики тиску з цифровим управлінням доцільно використовувати на пасажирських та транспортних...

-

Опис контактів процесора ADSP-BF534 - Розробка процесора ШПФ

Призначення контактів процесора ADSP-BF534 наведені в таблиці 1. З метою забезпечення максимальної функціональності та скорочення розміру корпусу і...

-

Тема роботи: Вивчення роботи регістрів. Мета роботи: Ознайомитись З Умовним графічним позначенням регістрів. Вивчити режими роботи регістру. Вивчити...

-

Характеристики процесора ADSP-BF534 - Розробка процесора ШПФ

Особливості: - Ядро ADSP-BF534 з частотою до 500 МГц; - Максимальна продуктивність, 1000 MMACS; - Три 16-розрядних помножувачі; - Два 40-розрядних АЛП; -...

-

Технологічний процес складання і контролю функціонування виробів PEA являє собою дуже складну систему, яка складається з множини функціональних одиниць і...

-

Пристрій виконаний за технологією поверхневого монтажу на друкованій платі із двостороннього скляного текстоліту розміром 200x135мм. Процес виготовлення...

-

Програмне забезпечення (ПЗ) є однією з важливих частин будь-якого обчислювального пристрою. Взагалі ПЗ являє собою сукупність програм, функціонально...

-

Вступ В приладах з радіо та електричними пристроями слабких струмів широко застосовується друкований монтаж - нанесення на поверхню основи, виготовленої...

-

Розробка технічного завдання - Створення комутаційної техніки на основі цифрових систем передачі

Для даного мікрорайону потрібно впровадити цифрову систему комутації (ЦСК) типу Квант-Є. Для початку розрахунку проектованої мережі потрібно визначитись...

-

Під надійністю розуміють властивість виробу виконувати завдання, функції, зберігати свої експлуатаційні показники в заданих межах на протязі необхідного...

-

Опис портів введення-виведення MS DOS може працювати з трьома паралельними пристроями (LPT1 - LPT3). Для підключення використовується стандартне...

-

Останнім часом зарубіжних системах зв'язку інтенсивно розвивається напрямок, пов'язаний з використанням так званих MIMO-технологій (Multiple Input -...

-

Правила установки крана для роботи Вимоги до місця установки крана для виконання робіт. Правила установки крана на виносні опори Майданчик, на який...

-

Роз'єднання туго посаджених деталей представляє значні труднощі, і крім того при цьому можна пошкодити роз'єднувальні деталі. Щоб при розбиранні не...

-

Ки. мс = Нмс/Нэрэ Где Нмс - общее количество микросхем и микросборок в изделии, шт. Нэрэ - общее количество электрорадиоэлементов, шт. Ки. мс = 29/251...

-

Так як використовується РКІ - Winstar WG12864A-NYJ, який має досить великі розміри, розмір друкованої плати обираємо таким же (93х70 мм) з отворами для...

-

За кордоном військові тропосферні лінії набули великого розвитку. Військові відомства США та інших країн НАТО, а також Японії активно застосовують...

-

Так як ми вже визначились зі структурною схемою приладу, то потрібно розробити електричну принципову. Спочатку визначимось з усіма складовими окремо. В...

-

Проведений аналіз якості продукції на підприємствах НВО "Персей" поданий у звіті (1-й етап), вивчення вітчизняних і закордонних матеріалів [6, 7]...

Аналіз блок-схеми виконання ШПФ - Розробка процесора ШПФ