Опис ядра процесора ADSP-BF534 - Розробка процесора ШПФ

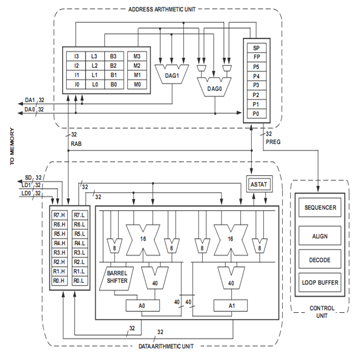

Ядро процесора ADSP-BF534 складається із двох 16-бітних помножувачів, двох 40-бітних акумуляторів, двох 40-бітних АЛП, чотирьох відео АЛП і з 40-бітного зсувного регістру. Процес обчислення відбувається над 8-, 16-, чи 32-бітними даними з регістрового файлу.

Регістровий файл вміщує вісім 32-бітних регістри. Коли здійснюються обчислювальні операції над 16-ти розрядними операндами, регістровий файл працює як 16 незалежних 16-ти розрядних регістрів. Всі операнди для комп'ютерних операцій завантажуються з багатопортового регістрового файлу і з полів вмісту інструкцій. Кожний помножувач може виконувати 16-ти розрядне множення в кожному циклі із накопиченням результатів у 40 розрядний акумулятор. Підтримуються знаковий і без знаковий формати даних, а також насичення і округлення.

АЛУ виконує традиційний набір арифметичних і логічних операцій над 16 (32) розрядними даними. А також підтримує багато спеціальних інструкцій для прискорення різних задач обробки сигналів. До них відносяться такі операції як вивільнення полів і визначення популяції, множення за модулем 232 , подільник примітивів, доповнення і заокруглення, а також визначення знаку/експоненти. Набір відео інструкцій включає: байт вирівнювання і упаковку операції, 16-бітні і 8-бітні додавання з відсіканням, 8-ми бітну операцію вирівнювання а також 8-ми бітну операцію віднімання/приведення до абсолютного значення/зберігання (SAA). Також є операції порівняння/вибору і векторного пошуку інструкцій. Для деяких інструкцій дві 16-бітні АЛП операції можуть виконуватись одночасно на регістрових парах.

Фур'є цифровий сигнальний мікропроцесор

Рис. 1.2 Ядро процесора Blackfin

Завдяки 40-бітному зсувному регістру можна здійснювати обертання і зсув, що використовується для нормалізації, розпакування полів та інструкцій упакування полів.

Програма секвенсор керує потоком виконання інструкцій, в тому числі інструкціями вирівнювання і декодування. Для програмного управління потоком, секвенсор підтримує ПК сумісні непрямі умовні переходи (зі статичним передбаченням розгалуження), і виклики підпрограм. Передбачене апаратурне виконання циклу нульових накладних. Архітектура є повністю закритою, це означає, що програмісту не потрібно керувати роботою конвеєру коли виконуються інструкції із взаємозалежними даними.

Модуль адресної арифметики володіє двома адресами, для одночасного подвійного вибору з пам'яті. Це означає, що багато портовий регістровий файл складається із чотирьох комплектів 32-бітових індексів, модифікації, довжини і базових регістрів (для кругової буферизації), і восьми додаткових 32 розрядних покажчиків регістрів (для С-типу індексування стекових маніпуляцій).

Процесор Blackfin підтримує модифіковану Гарвардську архітектуру в поєднанні із ієрархічною структурою пам'яті. Пам'ять першого рівня як зазвичай працює на тій же частоті, що й процесор. Пам'ять інструкцій першого рівня зберігає тільки інструкції. Дві пам'яті даних зберігають дані а також в специфічному блоці пам'яті зберігається стек та інформація локальних змінних. Окрім того кілька блоків пам'яті можна отримати конфігурацією і поєднанням SRAM та кешу. Модуль управління пам'яттю забезпечує захист пам'яті для окремих завдань, які можуть виконуватись на ядрі і може захищати системні регістри від ненавмисного доступу. Дана архітектура забезпечує три режими роботи: режим користувача, режим розробника а також режим емуляції. У користувацькому режимі обмежений доступ до певних режимів системи, забезпечуючи тим самим захист програмного середовища, в режимі розробника є необмежений доступ до систем і основних ресурсів. Набір інструкцій процесора Blackfin був оптимізований таким чином, що 16-ти бітові коди операцій є найбільш часто вживаними інструкціями, в результаті отримується скомпільований код відмінної щільності. Комплекс DSP інструкцій кодуються в 32-бітних кодах операцій, що представляють повнофункціональні інструкції багатофункціональними. Процесори Blackfin наділені обмеженими мультизадачними можливостями, де 32-бітова інструкція може бути видана одночасно з двох 16-бітних інструкцій, це дозволяє програмісту використовувати багато основних ресурсів ядра за один такт інструкції.

Мова налагодження процесора Blackfin використовує алгебраїчний синтаксис для полегшення кодування і читання. Архітектура оптимізована для використання спільно з С/С++ компіляторами, в результаті отримуємо швидке і ефективне написання програмного забезпечення.

Похожие статьи

-

2 Опис процесора ADSP-BF534 - Розробка процесора ШПФ

Процесор ADSP-BF534 являє собою процесор сімейства Blackfin з розширеними можливостями, тобто володіє більшою продуктивністю і меншою споживаною...

-

Архітектура пам'яті процесора ADSP-BF534 - Розробка процесора ШПФ

Процесор ADSP-BF534 розглядає пам'ять як один уніфікований 4 GB адресний простір, використовуючи 32-розрядну адресацію. Всі ресурси, в тому числі...

-

1 Розрахунок часу виконання - Розробка процесора ШПФ

Для розрахунку часу виконання алгоритму ШПФ на процесорі ADSP-BF525 потрібно визначити кількість операцій додавання, множення та читання/запису з/до...

-

Характеристики процесора ADSP-BF534 - Розробка процесора ШПФ

Особливості: - Ядро ADSP-BF534 з частотою до 500 МГц; - Максимальна продуктивність, 1000 MMACS; - Три 16-розрядних помножувачі; - Два 40-розрядних АЛП; -...

-

На пасажирських технічних станціях (або в технічних парках) проводять технічний і санітарний огляди, обмивання, очищення, санітарну обробку составів,...

-

Підключення вхідного інтерфейсу PPI, Підключення зовнішньої ПЗП типу EEPROM - Розробка процесора ШПФ

Programmable Peripheral Interface - двонаправлений напівдуплексний програмований інтерфейс периферійних пристроїв - використовують для зв'язку з...

-

Згідно технічного завданя необхідно розробити тракт ТА-А (АМ) й також ТА-Б (ПС). Функціональна схема з'єднувального тракту наведена в додатку Е. Умови...

-

Опис портів введення-виведення MS DOS може працювати з трьома паралельними пристроями (LPT1 - LPT3). Для підключення використовується стандартне...

-

Опис контактів процесора ADSP-BF534 - Розробка процесора ШПФ

Призначення контактів процесора ADSP-BF534 наведені в таблиці 1. З метою забезпечення максимальної функціональності та скорочення розміру корпусу і...

-

6 Застосування дискретного перетворення Фур'є - Розробка процесора ШПФ

1. Цифровий спектральний аналіз - Аналізатори спектра - Обробка мови - Обробка зображень - Розпізнавання образів 2. Проектування фільтрів - Обчислення...

-

Аналіз блок-схеми виконання ШПФ - Розробка процесора ШПФ

На рис.2.1 представлено обчислення ШПФ з використанням алгоритму з прорідженням за частотою з кількістю точок 1024. Цей метод потребує, щоб алгоритм...

-

Нижче наведена граф-схема алгоритму роботи програми. Рис. 5.1 Граф-схема алгоритму роботи програми Висновки Під час виконання курсового проекту було...

-

Підключення вихідного інтерфейсу SPI - Розробка процесора ШПФ

SPI ( Serial Peripheral Interface, SPI bus -- послідовний периферійний інтерфейс, шина SPI ) -- послідовний синхронний стандарт передачі даних в режимі...

-

Для міських станцій передбачається приміщення для клієнтів, площа якого приймається з розрахунку на 1 робочий пост: для СТОА до 15 постів -- 8...9 м2....

-

Швидке перетворення Фур'є - Розробка процесора ШПФ

Вихідними даними для ШПФ є елементи обмеженої послідовності x(n), де n=0,1,.. N-1. Відповідно дискретне перетворення Фур'є має вид: (1) (2) Де -...

-

Так як використовується РКІ - Winstar WG12864A-NYJ, який має досить великі розміри, розмір друкованої плати обираємо таким же (93х70 мм) з отворами для...

-

Робота блоку розпочинається з того, що центральний процесор формує на лініях КДА00-15Н адрес, він надходить на шинні формувачі (DD1-DD4), і при цьому...

-

Повністю схема функціональна подана у додатку. Нижче розписано основні аспекти стосовно розробки кожного окремого вузла. Розробка вузла синхронізації...

-

Рис.3 Блок-схема мікроконтроллеру ATtiny2313A/4313 ATtiny2313A/4313 - економічні 8-розрядні КМОП-мікроконтролери, виконані на основі покращеної...

-

Опис функціональної схеми модему - Захист інформації від витоку з телефонної мережі зв'язку

На рис. 7.2 представлена функціональна схема мікросхеми СМХ869, а в таблиці 7.1 наведено опис вхідних і вихідних сигналів. Рисунок 7.2 Функціональна...

-

Тема роботи: Вивчення роботи регістрів. Мета роботи: Ознайомитись З Умовним графічним позначенням регістрів. Вивчити режими роботи регістру. Вивчити...

-

Як вказано було вище, не будемо вдаватися в дискусію щодо того, яка з архітектур краще - CISCчи RISC, Гарвардська чи Прінстонська. Розглянемо відмінності...

-

Пристрій відрізняється від відомих вимірювачів температури на DS1820 можливістю одночасної регулювання температури в двох точках з точністю ± 0,5 ° в...

-

Так як ми вже визначились зі структурною схемою приладу, то потрібно розробити електричну принципову. Спочатку визначимось з усіма складовими окремо. В...

-

У запропонованій курсовому проекті описана будова і принцип дії системи живлення автомобіля c5. Викладено також основи його експлуатації, технічного...

-

Опис вибору елементної бази та роботи принципової схеми - Автоматичний регулятор температури

Схема терморегулятора показана на рис.7 (Додаток В). Резистором R8 встановлюють необхідну контрастність зображення індикатора. Всі блоки пристрою...

-

Методи налагодження пристрою Пристрій не вимагає налагодження, тому що він налагоджується при виготовлені його на заводах, перед початком експлуатації...

-

Програмна реалізація алгоритму роботи кондиціонера на мові асемблер для мікроконтролера AT89C51 представлена нижче. В основній програмі спочатку...

-

Мікропроцесор, Функції і будова мікропроцесора - Апаратні засоби ІВМ-сумісних

Мікропроцесор - центральний пристрій ЕОМ (або обчислювальної системи), що виконує арифметичні і логічні операції, задані програмою перетворення...

-

Опис принципової схеми Пульт керування Пульт керування кондиціонером містить два РКІ індикатора поточної температури приміщення і задається користувачем...

-

Для обгунтування власного технічного рішення робимо висновки з інформації наведеної в пункті 8. 1. Наявність в кондиціонері такої базової функції, як...

-

Сортувальні станції призначені для масової переробки вагонів, формування наскрізних, дільничних, збірних і передавальних поїздів. Одночасно на...

-

Кондиціювання повітря (лат. condicio умова, вимога) - це створення та автоматична підтримка (регулювання) в закритих приміщеннях всіх або окремих...

-

Розробка алгоритму роботи пристрою - Автоматичний регулятор температури

Після пуску та ініціалізації регістрів мікроконтролера виконується найтриваліша ініціалізація РК-дисплея. Далі перевіряється стан прапора установки. Якщо...

-

Опис об'єкта, для якого проектується мережа У даному дипломному проекті описується розробка мультисервісної мережі для Київського району м. Донецьк....

-

Моїм місцем для проходження практики була ПАФ "Петрівка", яка знаходиться в с. Петрівка Глобинського району Полтавської області. За час проходження...

-

Технології FTTx не накладають практично ніяких обмежень з точки зору пропускної спроможності і тому володіють відмінним запасом на майбутнє. Крім...

-

Визначається кількість абонентських модулів на ОПС і ПС, що відповідає числу ГТ до УКС. На станції застосовуються два типи модулів: абонентський модуль...

-

АНАЛІЗ ТЕХНІЧНОГО ЗАВДАННЯ, Функціональна схема мікроконтролера та її опис - Сучасні мікроконтролери

Функціональна схема мікроконтролера та її опис Нижче на рисунку 1.1 представлена схема використаного в курсовому проекті мікроконтролера ATtiny24....

-

РРС Р-415 призначена для створення тимчасових швидкорозгортаємих малоканальних радіорелейних ліній зв'язку, а також для відгалуження каналів від...

Опис ядра процесора ADSP-BF534 - Розробка процесора ШПФ