Архітектура мікроконтролерів сімейства AVR - Структурні особливості сучасних мікропроцесорних систем

Мікроконтролери ATmega є 8-розрядними CMOS мікроконтролерами з AVR удосконаленою RISC архітектурою. Виконуючи більшість команд за один тактовий цикл, мікроконтролери забезпечують продуктивність 1 MIPS на кожен мегагерц тактової частоти.

AVR ядро базується на удосконаленої RISC архітектурі, з реєстровим файлом швидкого доступу, що містить 32 регістра загального призначення, безпосередньо зв'язаних з АЛП, і могутньою системою команд. За один тактовий цикл із реєстрового файлу витягається два операнди, виконується команда і результат записується в регістр призначення. Така високоефективна архітектура забезпечує продуктивність майже в десять разів більшу, ніж стандартні CISС мікроконтролери.

Основною ідеєю всіх RISC, як відомо, є збільшення швидкодії за рахунок скорочення кількості операцій обміну з пам'яттю програм. Для цього кожну команду прагнуть умістити в одну комірку пам'яті програм. При обмеженій розрядності комірки пам'яті це неминуче приводить до скорочення набору команд мікропроцесора.

AVR мікроконтролери мають у своєму розпорядженні наступні можливості: 64 Кбайт внутрісистемно програмувальної Flash пам'яті програм, 2 Кбайта EEPROM даних, 4 Кбайта SRAM даних, 32 лінії уведення / виведення загального призначення, 32 робітників регістра загального призначення, 4 гнучких таймери/лічильника, UART, послідовний SPI порт.

Арифметико-логічний пристрій (АЛП), у якому виконуються всі обчислювальні операції, має доступ до тридцяти двох оперативних регістрів, об'єднаним у реєстровий файл. Вибірка вмісту регістрів, виконання операції і запис результату назад у реєстровий файл виконуються за один машинний цикл. Для порівняння корисно згадати, що більшість мікроконтролерів, що вбудовуються, мають тільки один такий регістр, безпосередньо доступний АЛП, - акумулятор, що вимагає включення в програму додаткових команд його завантаження і зчитування.

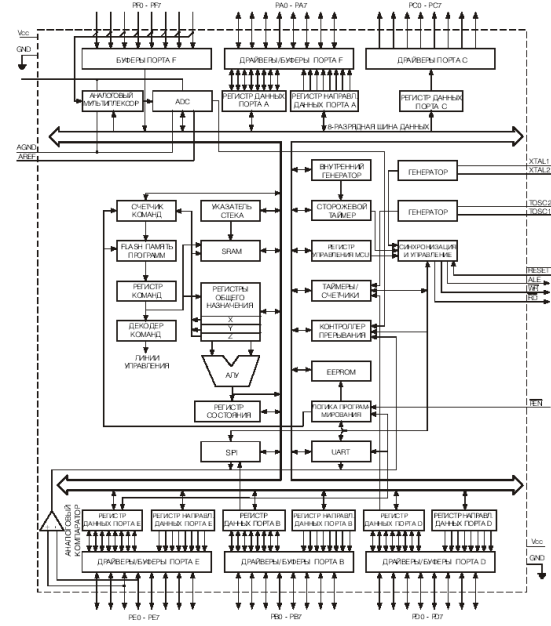

Рис. 1. Структурна схема мікроконтролера AVR

Організація пам'яті AVR виконана за схемою Гарвардського типу, у якій розділені не тільки адресні простори пам'яті програм і пам'яті даних, але також і шини доступу до них. Уся програмна пам'ять AVR-мікроконтролерів виконана за технологією FLASH і розміщена на кристалі. Вона являє собою послідовність 16-розрядних осередків і має ємність від 512 слів до 64K слів (тобто 16384 слів) у залежності від типу кристала.

В FLASH-пам'ять, крім програми, можуть бути записані постійні дані, що не змінюються під час функціонування мікропроцесорної системи. Це різні константи, таблиці знакогенераторів, таблиці лінеаризації датчиків і т. п.

Достоїнством технології FLASH є високий ступінь упакування, а недоліком те, що вона не дозволяє стирати окремі осередки. Тому завжди виконується повне очищення всієї пам'яті програм. При цьому для AVR гарантується, як мінімум, 1000 циклів перезапису FLASH-пам'яті.

Крім того, для збереження даних AVR-мікроконтролери можуть мати, у залежності від типу кристала, внутрішню (від 0 до 4Kбайт) і зовнішню (від 0 до 64 Кбайт) оперативну SRAM пам'ять і енергонезалежна внутрішню EEPROM пам'ять (від 0 до 4Kбайт).

Поділ шин доступу до FLASH пам'яті і SRAM пам'яті дає можливість мати шини даних для пам'яті даних і пам'яті програм різної розрядності, а також використовувати технологію конвеєризації. Конвеєризація полягає в тім, що під час виконання поточної команди програмний код наступної уже вибирається з пам'яті і дешифрується.

Для порівняння - у мікроконтролерів сімейства MCS-51 вибірка коду команди і її виконання здійснюються послідовно, що займає один машинний цикл, що триває 12 періодів кварцового резонатора.

Файл регістрів загального призначення. Усі реєстрові команди звертаються безпосередньо до регістрів у плині одного тактового циклу. Виключення складають п'ять логічних і арифметичних операцій з константами (SBCI, SUBI, CPI И и ANDI) і операція OR між константою і вмістом регістра, і команда безпосереднього завантаження LDI. Ці команди використовують другу половину регістрів реєстрового файлу - R16..R31. Шість регістрів реєстрового файлу, крім звичайної для інших регістрів функцій, виконують функцію 16-розрядних регістрів покажчиків адреси при непрямій адресації SRAM. Ці три регістри непрямої адресації визначаються як регістри X, Y і Z. У різних режимах адресації ці регістри виконують функції фіксованого зсуву, автоматичного инкременту і декременту.

Покажчик стека SP. Мікроконтролери AVR оснащені 16-розрядним покажчиком стека, розміщеним у двох регістрах простору I/O. Покажчик стека вказує на область у SRAM даних, у якій розміщаються стеки підпрограм і переривань. Обсяг стека повинна задаватися програмою перед кожним викликом підпрограми й обробкою дозволеного переривання.

Рівнобіжні порти уведення / виведення інформації. Мікроконтролер містить чотири 8-розрядних двонаправлені порти: PortA, PortB, PortC, PortD. До виходів портів можуть бути підключені убудовані навантажувальні резистори (окремо до кожного розряду). При використанні висновків цих чотирьох портів як входи й установці зовнішнім сигналом у низький стан, струм буде випливати тільки при підключених убудованих навантажувальних резисторах. Вихідні буфери порту A забезпечують струм, що втікає, 29 ма і здатні на пряму керувати LED індикатором. Порт B використовується при реалізації різних спеціальних функцій. Port - 8-розрядний порт висновку. Порт C використовуються також як виходи адреси при використанні зовнішньої пам'яті (SRAM). Port - 8-розрядний порт уведення. Входи порту також використовуються як аналогові входи аналого-цифрового перетворювача.

Таймери/лічильники. AVR мікроконтролери оснащені трьома таймерами/ лічильниками загального призначення - двома 8-розрядними й одним 16-розрядним. Таймер/лічильник0, на додаток до звичайного режиму, може тактується асинхронно від зовнішнього генератора, оснащений своїм власним попереднім дільником. Таймери/лічильники 1 і 2 використовують виходи ступіней розподілу загального 10-розрядного попереднього дільника. Ці два таймери/лічильника можна використовувати як таймери з убудованою базою або як лічильники, що переключаються за станом на зовнішньому висновку.

Попередній дільник таймерів/лічильників 1 і 2 містить чотири ступіні розподілу: СК/8, СК/64, СК/256 і СК/1024, де СК вхідний тактовий сигнал. Крім того як джерела тактових сигналів можуть бути використані сигнали від зовнішніх джерел, тактовий сигнал СК і нульовий тактовий сигнал (stop).

Точність і дозвіл 8-розрядних таймерів/лічильників росте зі зменшенням коефіцієнтів попереднього розподілу. Аналогічним образом високий коефіцієнт попереднього розподілу зручно використовувати при реалізації функцій з низькою швидкодією або точної синхронізації рідко відбуваються дій.

Послідовний периферійний інтерфейс (SPI) забезпечує високошвидкісний обмін даними між мікроконтролерами ATmega і периферійними пристроями або між декількома мікроконтролерами ATmega. SPI інтерфейс здійснює повнодуплексний 3-провідний синхронний обмін даними з переданими першим старшим або молодшим бітами, забезпечує чотири програмувальні швидкості передачі даних, виставляє прапор переривання по закінченні передачі.

Універсальний асинхронний приймально-передавач UART має наступні функції: висока швидкість передачі при низькій частоті XTAL, 8-розрядний або 9-розрядний формати даних, фільтрація шуму, виявлення переповнення, виявлення помилок формування кадрів.

Передача даних ініціюється записом переданих даних уведення / виведення UART. Дані пересилаються з UDR у регістр зсуву передачі в наступних випадках. Перший - новий символ записаний у UDR після того як був виведений з регістра стоповий біт попереднього символу. Регістр зсуву завантажується негайно. Другий - новий символ записаний у UDR перш, ніж був виведений стоповий біт попереднього символу. Регістр зсуву завантажується після виходу стопового біта попереднього символу, що знаходився у регістрі зсуву.

Керування роботою UART робить регістр даних UDR і регістр статусу USR і безпосередньо регістр керування UCR. У дійсності регістр UDR є двома фізично розділеними регістрами - регістром передачі даних і регістром прийому даних, що використовують ті самі адреси введення / висновку. При записі в регістр запис виробляється в регістр передачі даних UART, при читанні відбувається читання вмісту регістра прийому даних UART. Регістр USR забезпечує тільки читання інформації про стан UART. Установлюючи біти регістра UCR можна дозволяти глобальне переривання по завершенні прийому, установлювати 8-розрядний або 9-розрядний формат прийому або передачі.

Система переривань. Мікроконтролери ATmega використовують 23 джерела переривання. Ці переривання і вектор скидання розташовують окремими програмними векторами в просторі пам'яті програм. Кожному перериванню привласнений свій біт дозволу, що повинний бути встановлений разом з першим битому регістра статусу.

Переривання з молодшими адресами мають більший рівень пріоритету. RESET має найвищий рівень пріоритету, що випливає є INT0 - запит зовнішнього переривання 0 і т. д.

Мікроконтролери ATmega містять два спеціальних 8-розрядних регістри масок переривань: регістр масок зовнішніх переривань EIMSK і регістр масок переривань по таймері/лічильникові TIMSK. Крім того, у регістрах керування периферією можуть бути організовані й інші біти дозволу і біти масок.

Відгук на виконання всіх дозволених переривань AVR складає мінімум 4 тактових цикли. При обробці підпрограм переривань, що вимагають збереження, запис повинна виконуватися програмними засобами користувача. Для переривань запускаються статичними подіями прапор переривань встановлюється в момент настання події.

Похожие статьи

-

Архітектура PIC контролерів - Структурні особливості сучасних мікропроцесорних систем

PIC16fXX - це 8-розрядні FLASH CMOS мікроконтролери з RISC архітектурою, вироблені фірмою Microchip Technology. Це сімейство мікроконтролерів...

-

Архітектура контролерів серії C51 - Структурні особливості сучасних мікропроцесорних систем

В даний час серед усіх 8-розрядних мікроконтролерів - сімейство MCS-51 є безсумнівним чемпіоном з кількості різновидів і кількості компаній, що...

-

Особливості обробки сигналів в системі мобільного зв'язку з ЦДУ Як відомо, ємність СМЗ обумовлена кількістю абонентів, які вона може обслужити, є дуже...

-

Мікросхема К1816ВЕ48 являє собою НВІС однокристальної восьмирозрядної мікро-еом з вбудованою перепрограмованою пам'яттю (ППЗП), зі стиранням інформації...

-

ВСТУП - Сучасні мікроконтролери

ATMEL - один з світових лідерів у виробництві широкого спектру мікросхем незалежної пам'яті, FLASH-мікроконтролерів і мікросхем програмованої логіки,...

-

Стан сучасних розробок - Створення комутаційної техніки на основі цифрових систем передачі

Однією з плідних ідей розвитку сучасної системи комутації вважається концепція NGN (мережі зв'язку наступного покоління), що передбачає перехід на...

-

Выбор системы методом иерархий - Корпоративная система связи с использованием сетевой телефонии

Из всего множества систем выбираем 4 тех, которые имеют оптимальное соотношение между функциональными возможностями и стоимостью. Пусть, в результате...

-

Ансамбли сигналов в СПДС - Сигналы в системе преобразования дискретной связи

Сигнал в СПДС представляет собой изменяющуюся физическую величину, отображающую сообщение или его элементы. В общем виде сигнал на выходе УПС (устройства...

-

В результате сравнения производителей систем передач были выбраны две наиболее подходящие это система Cisco ONS 15808 и система ПУСК, выпущенная в России...

-

Первинні ЦСП - Типова апаратура цифрових систем передачі (ЦСП)

На первинній мережі використовуються 30-канальні первинні ЦСП з ІКМ: ІКМ-30, ІКМ-30С та їх модифікації. ЦСП ІКМ-30 призначена для організації зв'язку між...

-

Класифікація радіорелейних систем передачі - Засоби радіорелейного зв'язку

Існує безліч різних класифікацій радіорелейних систем передачі (РРСП) у залежності від ознак, покладених у їхню основу. За належністю до різних служб...

-

Frame Relay - Корпоративная система связи с использованием сетевой телефонии

Frame Relay (буквально: "передача кадров") - сравнительно новая и весьма перспективная технология передачи данных. Ее применение стало возможным...

-

Метод временного мультиплексирования (TDM) Суть TDM: процесс передачи разбивается на ряд временных циклов, каждый из которых в свою очередь разбивается...

-

Опис функціональної схеми модему - Захист інформації від витоку з телефонної мережі зв'язку

На рис. 7.2 представлена функціональна схема мікросхеми СМХ869, а в таблиці 7.1 наведено опис вхідних і вихідних сигналів. Рисунок 7.2 Функціональна...

-

МікроЕОМ серії К1814 являють собою чотирирозрядні ОМЕОМ, призначені для побудови різних систем керування. До складу серії входить універсальна мікро-еом...

-

Рис.3 Блок-схема мікроконтроллеру ATtiny2313A/4313 ATtiny2313A/4313 - економічні 8-розрядні КМОП-мікроконтролери, виконані на основі покращеної...

-

З погляду виробників мікропроцесорної техніки всі задачі, вирішувані системами вбудованого управління, поділяються на два великі класи: управління...

-

Опис портів введення-виведення MS DOS може працювати з трьома паралельними пристроями (LPT1 - LPT3). Для підключення використовується стандартне...

-

AT90S2313 - економічний 8 бітовий КМОН-мікроконтролер, побудований з використанням розширеної RISC архітектури AVR. Виконуючи по одній команді за період...

-

Принципы построения ВОСПИ Оптические волокна производятся разными способами, они обеспечивают передачу оптического излучения на разных длинах волн, имеют...

-

Принцип спектрального уплотнения (WDM) Потенциальные ресурсы волокна. До настоящего времени на многих коммерческих линиях использовалась скорость...

-

В системе TANGARA RD применяется цифровой метод FDMA (частотное разделение каналов), совмещенный с TDD. Схема используемой модуляции - GFSK (частотная...

-

Анализ путей решения поставленной задачи Постановка задачи следующая: необходимо в несколько раз повысить пропускную способность магистральной ВОЛС...

-

Беспроводные сети - Корпоративная система связи с использованием сетевой телефонии

Технология передачи информации между абонентами, находящимися друг от друга на значительных расстояниях, постепенно, но уверенно, переходит с рельс...

-

Схема управления и интерфейс - Разработка профессионального радиопередатчика систем низовой связи

Схема управления основана на микроконтроллере PIC16C63. Основные характеристики данной микросхемы перечислены в предыдущем пункте. Работа процессора...

-

Назначение: Организации доступа к сетям различного уровня по медной паре. Наиболее эффективно подходит для организации доступа к всемирной сети Интернет....

-

Цель и постановка задачи - Мехатронные системы автомобильного транспорта

То определяющее значение, которое принадлежит электронной системе в автомобиле, заставляет уделять повышенное внимание проблемам, связанным с их...

-

Обслуживание с ожиданием - Теория систем массового обслуживания

Постановка задачи СМО с ожиданием распространены наиболее широко. Их можно разбить на 2 большие группы - Разомкнутые и Замкнутые . Эти системы определяют...

-

Разработка функциональной схемы опорного пункта (ОП) Оборудование выполнено в виде стоек, устанавливаемых в пунктах волоконно-оптической линии передачи:...

-

Останнім часом зарубіжних системах зв'язку інтенсивно розвивається напрямок, пов'язаний з використанням так званих MIMO-технологій (Multiple Input -...

-

Основы линейного кодирования. Полученный в результате квантования и двоичного кодирования цифровой поток оптимален с точки зрения ошибок квантования, но...

-

Выбор типа источника излучения и фотоприемника, их параметры Выбор типа источника излучения. Общие требования к источникам излучения ВОСП следующие: л...

-

ВВЕДЕНИЕ, Системы визуального отображения информации (видеосистемы) - Внешние устройства ЭВМ

Персональный компьютер (ПК)- это не один электронный аппарат, а Небольшой комплекс взаимосвязанных устройств, каждое из которых выполняет определенные...

-

Автоматическая телефонная станция декадно-шагового типа - Системы телекоммуникации

Рассмотрим принцип построения декадно-шаговых АТС на нескольких примерах. Используя только одну ступень - ступень линейного искания Рисунок 17 Упрощенная...

-

Особливості IP-телебачення - IP-телебачення: сучасний стан, перспективи розвитку

Для реалізації технології IP-телебачення необхідна сучасна мультисервісна інфраструктура, що складається з мереж доступу, транспортної мережі, головної...

-

Итак, пробок можно избежать, а пропускную способность магистрали можно увеличить многократно за счет изменения пространственного расположения полос...

-

ПОМЕХОУСТОЙЧИВОЕ КОДИРОВАНИЕ - Расчет параметров системы передачи дискретных сообщений

В связи с тем, что при приеме сообщений необходимо обеспечить вероятность ошибки не более 10-6 , используются помехоустойчивые коды, исправляющая и...

-

Система селективного нагрева ионов в установке "Плазменный сепаратор-1"

Описание экспериментальной установки ПС - 1 Для большей наглядности и лучшего понимания процесса ВЧ - нагрева плазмы в установке ПС - 1 опишу вкратце всю...

-

В соответствии с исходными данными варианта в качестве приемника применяется приемник когерентного приема ДЧМ. Рассмотрим выражение временной функции...

-

ВВЕДЕНИЕ - Проект обобщенной структурной схемы системы передачи сообщений

Теория электрической связи (ТЭС), можно сказать, является первым специальным курсом, который ведет к дальнейшему изучению специальности. ТЭС -...

Архітектура мікроконтролерів сімейства AVR - Структурні особливості сучасних мікропроцесорних систем