Архітектура контролерів серії C51 - Структурні особливості сучасних мікропроцесорних систем

В даний час серед усіх 8-розрядних мікроконтролерів - сімейство MCS-51 є безсумнівним чемпіоном з кількості різновидів і кількості компаній, що випускають його модифікації. Воно одержало свою назву від першого представника цього сімейства - мікроконтролера 8051, випущеного в 1980 році на базі технології HMOS. Удалий набір периферійних пристроїв, можливість гнучкого вибору зовнішньої або внутрішньої програмної пам'яті і прийнятна ціна забезпечили цьому мікроконтролерові успіх на ринку.

У результаті на сьогоднішній день існує більш 200 модифікацій мікроконтролерів сімейства 8051, що випускаються майже 20-ю компаніями. Ці модифікації містять у собі кристали з найширшим спектром периферії: від простих 20-вивідних пристроїв з одним таймером і 1K програмної пам'яті до складних 100-вивідних кристалів з 10-розрядними АЦП, масивами таймерів-лічильників, апаратними 16-розрядними множення і 64K програмної пам'яті на кристалі. Щороку з'являються всі нові варіанти представників цього сімейства. Основними напрямками розвитку є: збільшення швидкодії (підвищення тактової частоти і переробка архітектури), зниження напруги харчування і споживання, збільшення обсягу ОЗП і FLASH пам'яті на кристалі з можливістю внутрісхемного програмування, уведення до складу периферії мікроконтролера складних пристроїв типу системи керування приводами, CAN і USB інтерфейсів і т. п.

Усі мікроконтролери із сімейства MCS-51 мають загальну систему команд. Наявність додаткового устаткування впливає тільки на кількість регістрів спеціального призначення. Система команд MCS-51, орієнтована на реалізацію різних цифрових алгоритмів керування і має деякі переваги:

Біто-біто-орієнтовані операції та адресовані в пам'яті даних бітові поля, що дало можливість говорити про реалізації на кристалі бітового процесора;

Реалізовано виконання команд множення, розподіли і вирахування;

Удосконалено роботу зі стеком;

Розширено групу команд передачі керування;

Введення апаратного послідовного дуплексного порту;

Дворівнева система переривань.

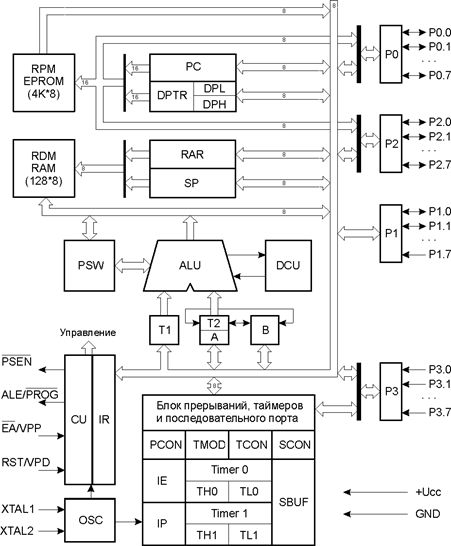

Мікроконтролер MCS-51 виконаний на основі багаторівневій n-МОП технології. Через чотири програмувальних рівнобіжних порти уведення / виведення й один послідовний порт мікроконтролер взаємодіє з зовнішніми пристроями. Основу структурної схеми (мал. 1) утворить внутрішня двонаправлена 8-бітна шина, що зв'язує між собою основні вузли і пристрої мікроконтролера: резидентну пам'ять програм (RPM), резидентну пам'ять даних (RDM), арифметико-логічний пристрій (АЛП), блок регістрів спеціальних функцій, пристрій керування (CU) і порти уведення / виведення (P0-P3).

Рис. 2. Структурна схема мікроконтролера MCS-51

АЛП - 8-бітний арифметико-логічний пристрій (АЛП) може виконувати арифметичні операції додавання, вирахування, множення і розподіли; логічні операції И, АБО, що виключає АБО, а також операції циклічного зрушення, скидання, інвертування і т. п. До входів підключені програмно-недоступні регістри T1 і T2, призначені для тимчасового збереження операндів, схема десяткової корекції (DCU) і схема формування ознак результату операції (PSW).

Найпростіша операція додавання використовується в АЛП для інкрементування вмісту регістрів, просування регістра-покажчика даних (RAR) і автоматичного обчислення наступної адреси резидентної пам'яті програм. Найпростіша операція вирахування використовується в АЛП для декрементування регістрів і порівняння перемінних.

Важливою особливістю АЛП є його здатність оперувати не тільки байтами, але і бітами. Окремі програмно-доступні біти можуть бути встановлені, скинуті, інвертовані, передані, перевірені і використані в логічних операціях. Ця здатність досить важлива, оскільки для керування об'єктами часто застосовуються алгоритми, що містять операції над вхідними і вихідними булевими перемінними, реалізація яких засобами звичайних мікропроцесорів сполучена з визначеними труднощами.

Таким чином, АЛП може оперувати чотирма типами інформаційних об'єктів: булевими (1 біт), цифровими (4 біти), байтними (8 біт) і адресними (16 біт). У АЛП виконується 51 різна операція пересилання або перетворення цих даних. Тому що використовується 11 режимів адресації (7 для даних і 4 для адрес), те шляхом комбінування операції і режиму адресації базове число команд 111 розширюється до 255 з 256 можливих при однобайтному коді операції.

Резидентна пам'ять програм і даних. Резидентні (розміщені на кристалі) пам'ять програм (RPM) і пам'ять даних (RDM) фізично і логічно розділені, мають різні механізми адресації, працюють під керуванням різних сигналів і виконують різні функції.

Пам'ять програм RPM має ємність 4 Кбайта і призначена для збереження команд, констант, що керують слів ініціалізації, таблиць перекодування вхідна і вихідна перемінних і т. п. Пам'ять має 16-бітну шину адреси, через яку забезпечується доступ із програмного лічильника PC або з регістра-покажчика даних (DPTR). DPTR виконує функції базового регістра при непрямих переходах по програмі або використовується в операціях з таблицями.

Пам'ять даних RDM призначена для збереження перемінних у процесі виконання прикладної програми, адресується одним байтом і має ємність128 байт. Крім того, до її адресного простору примикають адреси регістрів спеціальних функцій, що перераховані в табл. 1.

Пам'ять програм, так само як і пам'ять даних, може бути розширена до 64 Кбайт шляхом підключення зовнішніх мікросхем.

Акумулятор, регістри загального призначення і прапори. Акумулятор (A) є джерелом операнду і місцем фіксації результату при виконанні арифметичних, логічних операцій і ряду операцій передачі даних. Крім того, тільки з використанням акумулятора можуть бути виконані операції зрушень, перевірка на нуль, формування прапора паритету і т. п. У розпорядженні користувача маються 8 регістрів загального призначення R0-R7 одного з чотирьох можливих банків. При виконанні багатьох команд у АЛП формується ряд ознак операції (прапорів), що фіксуються в регістрі PSW.

Найбільше "активним" прапором PSW є прапор переносу, що бере участь і модифікується в процесі виконання безлічі операцій, включаючи додавання, вирахування і зрушення. Крім того, прапор переносу (C) виконує функції "булевого акумулятора" у командах, що маніпулюють з бітами. Прапор переповнення (OV) фіксує арифметичне переповнення при операціях над цілими числами зі знаком і уможливлює використання арифметики в додаткових кодах. АЛП не керує прапорами селекції банку регістрів (RS0, RS1), їхнє значення цілком визначається прикладною програмою і використовується для вибору одного з чотирьох реєстрових банків.

У мікропроцесорах, архітектура яких спирається на акумулятор, більшість команд працюють з ним, використовуючи неявну адресацію. У Intel 8051 справа обстоїть інакше. Хоча процесор має у своїй основі акумулятор, він може виконувати безліч команд і без його участі. Наприклад, дані можуть бути передані з будь-якого осередку RDM у будь-який регістр, будь-який регістр може бути завантажений безпосереднім операндом і т. д. Багато логічних операцій можуть бути виконані без участі акумулятора. Крім того, перемінні можуть бути інкрементованими, декрементованими і перевірені без використання акумулятора. Прапори і керуючі біти можуть бути перевірені і змінені аналогічно.

Регістри-покажчики. 8-бітний покажчик стека (SP) може адресувати будь-яка область RDM. Його вміст інкрементируеться перш, ніж дані будуть запам'ятовані в стеці в ході виконання команд PUSH і CALL. Уміст SP декрементуеться після виконання команд POP і RET. Подібний спосіб адресації елементів стека називають передінкрементним/постдекрементним. У процесі ініціалізації мікроконтролера після сигналу RST у SP автоматично завантажується код 07Н. Це значить, що якщо прикладна програма не перевизначає стек, те перший елемент даних у стеці буде розташовуватися в осередку RDM з адресою 08Н.

Двухбайтнтий регістр-покажчик даних DPTR звичайно використовується для фіксації 16-бітної адреси в операціях зі звертанням до зовнішньої пам'яті. Командами мікроконтролера регістр-покажчик даних може бути використаний або як 16-бітний регістр, або як два незалежних 8-бітних регістри (DPH і DPL).

Регістри спеціальних функцій. Регістри із символічними іменами IP, IE, TMOD, TCON, SCON і PCON використовуються для фіксації і програмної зміни керуючих біт і біт стану схеми переривання, таймера/лічильника, приймача-передавача послідовного порту і для керування енергоспоживанням. Їхня організація буде описана нижче при розгляді особливостей роботи мікроконтролера в різних режимах.

Пристрій керування і синхронізації. Кварцовий резонатор, що підключається до зовнішніх висновків мікроконтролера, керує роботою внутрішнього генератора, що у свою чергу формує сигнали синхронізації. Пристрій керування (CU) на основі сигналів синхронізації формує машинний цикл фіксованої тривалості, рівним 12 періодам резонатора. Більшість команд мікроконтролера виконується за один машинний цикл. Деякі команди, що оперують з 2-байтними словами або зв'язані зі звертанням до зовнішньої пам'яті, виконуються за два машинних цикли. Тільки команди розподілу і множення вимагають чотирьох машинних циклів. На основі цих особливостей роботи пристрою керування виробляється розрахунок часу виконання прикладних програм.

На схемі мікроконтролера до пристрою керування примикає регістр команд (IR). У його функцію входить збереження коду виконуваної команди.

Рівнобіжні порти уведення / виведення інформації. Усі чотири порти (P0-P3) призначені для введення або висновку інформації побайтно. Кожен порт містить керований регістр-засувку, вхідний буфер і вихідний драйвер.

Вихідні драйвери портів 0 і 2, а також вхідний буфер порту 0 використовуються при звертанні до зовнішньої пам'яті. При цьому через порт 0 у режимі тимчасового мультиплексировання спочатку виводиться молодший байт адреси, а потім видається або приймається байт даних. Через порт 2 виводиться старший байт адреси в тих випадках, коли розрядність адреси дорівнює 16 біт. Усі висновки порту 3 можуть бути використані для реалізації альтернативних функцій, перерахованих у табл. 4. Ці функції можуть бути задіяні шляхом запису 1 у відповідні біти регістра-засувки (P3.0-P3.7) порту 3. Порт 0 є двонаправленим, а порти 1-3 - квазидвонаправленими. Кожна лінія портів може бути використана незалежно для введення або висновку.

По сигналі RST у регістри-засувки всіх портів автоматично записуються одиниці, що набудовують їх тим самим на режим уведення.

Звертання до портів уведення / виведення можливо з використанням команд, що оперують з байтом, окремим бітом, довільною комбінацією бітов.

Таймер/лічильник. У складі мікроконтролера маються реєстрові пари із символічними іменами TH0, TL0 і TH1, TL1, на основі яких функціонують два незалежних програмно-керованих 16-бітних таймери/лічильника подій (T/C0 і T/C1). При роботі як таймер уміст T/C інкрементується в кожнім машинному циклі, тобто через кожні 12 періодів резонатора. При роботі як лічильник уміст T/C інкрементується під впливом переходу з 1 у 0 зовнішнього вхідного сигналу, подаваного на відповідний (T0, T1) вхід мікроконтролера. Опитування сигналів виконується в кожнім машинному циклі. Тому що на розпізнавання переходу потрібно два машинних цикли, те максимальна частота підрахунку вхідних сигналів дорівнює 1/24 частоти резонатора. На тривалість періоду вхідних сигналів обмежень зверху немає. Для гарантованого прочитання вхідного сигналу, що зчитується, він повинний утримувати значення 1 як мінімум протягом одного машинного циклу.

Для керування режимами роботи і для організації взаємодії таймерів із системою переривання використовуються два регістри спеціальних функцій TMOD і TCON.

Послідовний порт. Через універсальний асинхронний приймач-передавач UART (Universal Asynchronous Receiver-Transmitter) відбувається передача інформації, представленої послідовним кодом (молодшими бітами вперед), у повному дуплексному режимі обміну. До складу UART, називаного часто послідовним портом, входять приймаючий і передавальний що зрушують регістри, а також спеціальний буферний регістр (SBUF) приймача-передавача, що являє собою два незалежних регістри: буфер приймача і буфер передавача. Завантаження байта в SBUF негайно викликає початок процесу передачі через послідовний порт. Коли байт зчитується з SBUF, це значить, що його джерелом є приймач послідовного порту. Запис байта в буфер приводить до автоматичного перепису байта в регістр передавача, що зрушує, і ініціює початок передачі байта. Наявність буферного регістра приймача дозволяє сполучати операцію читання раніше прийнятого байта з прийомом чергового байта. Якщо до моменту закінчення прийому байта попередній байт не був лічений, то він буде загублений.

Послідовний порт може працювати в чотирьох різних режимах.

Режим 0. Інформація передається і приймається через вхід приймача RXD. Приймаються і передаються 8 біт даних. Через зовнішній вихід передавача TXD видаються імпульси зрушення, що супроводжують кожен біт. Частота передачі дорівнює 1/12 частоти резонатора.

Режим 1. Через TXD передаються або з RXD приймаються 10 біт: старт-битий (0), 8 біт даних і стоп-битий (1). Швидкість прийому/передачі - величина перемінна і задається таймером.

Режим 2. Через TXD передаються або з RXD приймаються 11 біт: старт-битий, 8 біт даних, програмувальний дев'ятий біт і стоп-битий. При передачі дев'ятий біт може використовуватися для підвищення вірогідності передачі шляхом контролю по парності й у нього можна помістити значення ознаки паритету з PSW. Частота прийому/передачі вибирається програмно і може бути дорівнює 1/32 або 1/64 частоти резонатора в залежності від SMOD.

Режим 3. Збігається з режимом 2, але частота прийому/передачі є величиною перемінної і задається таймером.

Система переривань.

Зовнішні переривання INT0 і INT1 можуть бути викликані рівнем або переходом сигналу з 1 у 0 на входах мікроконтролера в залежності від значень керуючих бітів IT0 і IT1 у регістрі TCON. Від зовнішніх переривань установлюються прапори IE0 і IE1 у регістрі TCON, що ініціюють виклик відповідної підпрограми обслуговування переривання. Скидання цих прапорів виконується апаратно тільки в тому випадку, якщо переривання було викликано по переходу (зрізові) сигналу. Якщо ж переривання викликане рівнем вхідного сигналу, то скиданням прапора IE керує відповідна підпрограма обслуговування переривання шляхом впливу на джерело переривання з метою зняття їм запиту.

Прапори запитів переривання від таймерів TF0 і TF1 скидаються автоматично при передачі керування підпрограмі обслуговування. Прапори запитів переривання RI і TI установлюються UART апаратно, але скидатися повинні програмою. Переривання можуть бути викликані або скасовані програмою, тому що всі перераховані прапори програмно доступні.

Можливість програмної установки / скидання будь-якого керуючого біта в цих двох регістрах робить систему переривань винятково гнучкої.

Прапори переривань опитуються в кожнім машинному циклі. Ранжирування переривань по пріоритеті виконується протягом наступного машинного циклу. Система переривань сформує апаратно виклик LCALL відповідної підпрограми обслуговування, якщо вона не заблокована.

Мікроконтролер пам'ять регістр інтерфейс

Похожие статьи

-

Архітектура PIC контролерів - Структурні особливості сучасних мікропроцесорних систем

PIC16fXX - це 8-розрядні FLASH CMOS мікроконтролери з RISC архітектурою, вироблені фірмою Microchip Technology. Це сімейство мікроконтролерів...

-

Архітектура мікроконтролерів сімейства AVR - Структурні особливості сучасних мікропроцесорних систем

Мікроконтролери ATmega є 8-розрядними CMOS мікроконтролерами з AVR удосконаленою RISC архітектурою. Виконуючи більшість команд за один тактовий цикл,...

-

Особливості обробки сигналів в системі мобільного зв'язку з ЦДУ Як відомо, ємність СМЗ обумовлена кількістю абонентів, які вона може обслужити, є дуже...

-

Мікросхема К1816ВЕ48 являє собою НВІС однокристальної восьмирозрядної мікро-еом з вбудованою перепрограмованою пам'яттю (ППЗП), зі стиранням інформації...

-

Визначення структури і складу системи керування робиться за допомогою конфігуратора HW Config , який є складовою частиною язика програмування. Він...

-

Опис функціональної схеми модему - Захист інформації від витоку з телефонної мережі зв'язку

На рис. 7.2 представлена функціональна схема мікросхеми СМХ869, а в таблиці 7.1 наведено опис вхідних і вихідних сигналів. Рисунок 7.2 Функціональна...

-

Для визначення положення використовуются абсолютні датчики положення, які видають код кута обертання і не потребуют визначення початкового значення...

-

Промислові мережі - інтегровані, відкриті промислові комунікації. Промисловий Ethernet (IEEE 802. 3) міжнародний стандарт для мереж що мають як...

-

МікроЕОМ серії К1814 являють собою чотирирозрядні ОМЕОМ, призначені для побудови різних систем керування. До складу серії входить універсальна мікро-еом...

-

Останнім часом зарубіжних системах зв'язку інтенсивно розвивається напрямок, пов'язаний з використанням так званих MIMO-технологій (Multiple Input -...

-

Особливості кристалічної структури Аналіз вже наявних відомостей про будову і склад ВТНП дозволив зробити ряд узагальнень. По-перше, практично всі вони є...

-

Важливою первагою сучасних частотних перетворювачів є можливість керування за допомогою локальноїй мережі. Так керування частотними перетворювачами...

-

Складання проекту системи керування [7, c. 3-6 - 3-8] Мова програмування програмованих контролерів, наприклад, STEP7 фірми SIEMENS, включає засоби...

-

З погляду виробників мікропроцесорної техніки всі задачі, вирішувані системами вбудованого управління, поділяються на два великі класи: управління...

-

Стан сучасних розробок - Створення комутаційної техніки на основі цифрових систем передачі

Однією з плідних ідей розвитку сучасної системи комутації вважається концепція NGN (мережі зв'язку наступного покоління), що передбачає перехід на...

-

Так як ми вже визначились зі структурною схемою приладу, то потрібно розробити електричну принципову. Спочатку визначимось з усіма складовими окремо. В...

-

Класифікація радіорелейних систем передачі - Засоби радіорелейного зв'язку

Існує безліч різних класифікацій радіорелейних систем передачі (РРСП) у залежності від ознак, покладених у їхню основу. За належністю до різних служб...

-

В результате сравнения производителей систем передач были выбраны две наиболее подходящие это система Cisco ONS 15808 и система ПУСК, выпущенная в России...

-

Разработка функциональной схемы опорного пункта (ОП) Оборудование выполнено в виде стоек, устанавливаемых в пунктах волоконно-оптической линии передачи:...

-

Класифікація і структура ергономічних вимог Ергономічне забезпечення грунтується на ЕВ, що є вихідними при проведенні проектної роботи. Вони визначаються...

-

ВВЕДЕНИЕ - Проект обобщенной структурной схемы системы передачи сообщений

Теория электрической связи (ТЭС), можно сказать, является первым специальным курсом, который ведет к дальнейшему изучению специальности. ТЭС -...

-

Основы линейного кодирования. Полученный в результате квантования и двоичного кодирования цифровой поток оптимален с точки зрения ошибок квантования, но...

-

Гнучкий мультиплексор Т-130 - Типова апаратура цифрових систем передачі (ЦСП)

Телефонна станція мультиплексор цифровий Гнучкий мультиплексор Т-130 входить до складу апаратури первинної ЦСП ІКМ-30- Він забезпечує ущільнення до 30...

-

Первинні ЦСП - Типова апаратура цифрових систем передачі (ЦСП)

На первинній мережі використовуються 30-канальні первинні ЦСП з ІКМ: ІКМ-30, ІКМ-30С та їх модифікації. ЦСП ІКМ-30 призначена для організації зв'язку між...

-

Розробка технічного завдання - Створення комутаційної техніки на основі цифрових систем передачі

Для даного мікрорайону потрібно впровадити цифрову систему комутації (ЦСК) типу Квант-Є. Для початку розрахунку проектованої мережі потрібно визначитись...

-

Ансамбли сигналов в СПДС - Сигналы в системе преобразования дискретной связи

Сигнал в СПДС представляет собой изменяющуюся физическую величину, отображающую сообщение или его элементы. В общем виде сигнал на выходе УПС (устройства...

-

Для начала рассмотрим плезиохронную иерархию (PDH), она явилась предпосылкой к появлению синхронной цифровой иерархии (SDH): 1) Принята в США и Канаде. В...

-

Выбор типа источника излучения и фотоприемника, их параметры Выбор типа источника излучения. Общие требования к источникам излучения ВОСП следующие: л...

-

Особливості IP-телебачення - IP-телебачення: сучасний стан, перспективи розвитку

Для реалізації технології IP-телебачення необхідна сучасна мультисервісна інфраструктура, що складається з мереж доступу, транспортної мережі, головної...

-

Як вказано було вище, не будемо вдаватися в дискусію щодо того, яка з архітектур краще - CISCчи RISC, Гарвардська чи Прінстонська. Розглянемо відмінності...

-

W-CDMA в системах третього покоління - Дослідження мереж передачі даних на базі технології W-CDMA

Аналогові стільникові системи зазвичай називаються системами першого покоління. Цифрові системи, що знаходяться у використанні в даний час, такі як GSM,...

-

Беспроводные сети - Корпоративная система связи с использованием сетевой телефонии

Технология передачи информации между абонентами, находящимися друг от друга на значительных расстояниях, постепенно, но уверенно, переходит с рельс...

-

Для моделювання на ЕОМ компонентів КС, сконструйованих із нейронів усвідомлена необхідність у спеціальному інструменті, що дозволяє за допомогою зручного...

-

Вступ - Використання нейромережевих технологій при створенні систем підтримки прийняття рішень

При сучасному рівні розвитки техніки, коли навіть побутова техніка обладнується мікропроцесорними пристроями, виникнула потреба в інтелектуальних...

-

Принципы построения ВОСПИ Оптические волокна производятся разными способами, они обеспечивают передачу оптического излучения на разных длинах волн, имеют...

-

Опис портів введення-виведення MS DOS може працювати з трьома паралельними пристроями (LPT1 - LPT3). Для підключення використовується стандартне...

-

Література - Проектування систем керування на основі програмованих логічних контролерів

1. Цифрова техніка: Учеб. пособие /Б. Е.Рыцар. Киев: УМК ВО, 1991 - 372 с. На укр. яз. (4 прим.) 2. Элементы автоматизированного электропривода / Р....

-

УКХ радіоустановка з радіотелефоном і ЦВВ - Радіоустаткування морського транспорту

Радіостанція аварійний антена сигнал УКХ радіоустановка забезпечує радіотелефонний зв'язок і цифровий вибірковий виклик на відстані 20-30 морських миль....

-

Пристрій відрізняється від відомих вимірювачів температури на DS1820 можливістю одночасної регулювання температури в двох точках з точністю ± 0,5 ° в...

-

Рекомендації щодо використання вітчизняної елементної бази - Реалізації технології ЦДУ

Повнота реалізації переваг ЦАР багато в чому залежить від якісних параметрів елементної бази. Прогрес у розвитку мікропроцесорної техніки і теорії ЦОС...

Архітектура контролерів серії C51 - Структурні особливості сучасних мікропроцесорних систем