ЭНЕРГОНЕЗАВИСИМАЯ ПАМЯТЬ (NVSRAM), УВЕЛИЧЕНИЕ РАЗРЯДНОСТИ ЯЧЕЙКИ ПАМЯТИ (СЛОВА), УВЕЛИЧЕНИЕ КОЛИЧЕСТВА ЯЧЕЕК ПАМЯТИ - Цифровые устройства и микропроцессоры

Всякая память сохраняющая данные при отключении внешнего источника питания может считаться энергонезависимой - NonVolatile Memory, однако этот термин больше утвердился за статической оперативной памятью:

- ? с встроенной в микросхему литиевой батарейкой большой емкости. ? с дополнительной EEPROM на том же кристалле, причем обмен данными между SRAM и EEPROM производится либо программно либо автоматически при падении/восстановлении напряжения

УВЕЛИЧЕНИЕ РАЗРЯДНОСТИ ЯЧЕЙКИ ПАМЯТИ (СЛОВА)

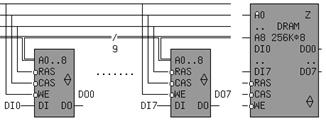

Если требуется хранить данные размером в n-бит, а длина слова ячейки памяти m-бит (n>m), то прибегают к наращиванию длины слова. Делается это путем объединения n/m - микросхем в группы, причем все одноименные входы, кроме информационных, соединяются между собой. Например, если требуется динамическая память емкостью 256K с длиной слова равной байту, то необходимо объединить 8 / 1 = 8 микросхем типа 565РУ7, как это показано на рис.

На рисунке девять линий адреса показаны в виде шины - т. е. группы проводников, объединенных по функциональному признаку.

УВЕЛИЧЕНИЕ КОЛИЧЕСТВА ЯЧЕЕК ПАМЯТИ

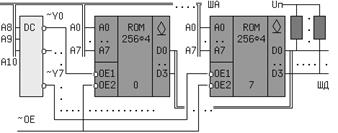

Увеличение адресного пространства ЗУ в 2k раз требует столько же микросхем памяти и "k" дополнительных линий адреса, к уже имеющимся "n"линиям An+k-1, . .An+0, An-1, An-2, ... A1, A0. Дополнительные адресные линии An+k-1 .. An+0 должны разбивать требуемое адресное поле на 2k неперекрывающихся интервалов, покрываемых объемом памяти каждой отдельной микросхемы. Для решения этой задачи требуется дополнительный дешифратор "k в 2k". Например, если нужен блок ПЗУ емкостью 2K*4, то потребуется 8 микросхем 256*4 типа 541РТ1 и один дешифратор "3 в 8", как показано на рис.

Одноименные j - е выходы микросхем с открытым коллектором соединены с общим нагрузочным резистором Rj. Три старших дополнительных бита адреса A10,A9,A8 выбирают одну из восьми микросхем, а восемь младших бит адреса выводят содержимое одной из 256-ти ячеек памяти на шину данных (ШД).Пусть на шину адреса (ША) поступил код A10..A0 = 11000011010 = 61A. На всех выходах дешифратора, кроме шестого (A10..A8 = 110 =6) будет высокий уровень. Нулевой сигнал ~Y6 = 0 на входе ~OE1 шестой микросхемы разрешит прохождение записанной информации на выходы, а код 1 1010 = 1A(HEX) = 26(DEC) на адресных входах A7..A0 извлечет содержимое 26-ой ЯП и поместит его на четыре линии шины данных (ШД).

Особенностью метода является необходимость объединения по ИЛИ(И) одноименных выходов микросхем. Это можно выполнить или подключением одноименных выходов к 2n - входовым схемам ИЛИ(И) для каждого разряда, или выполнять выходные структуры микросхем памяти по схеме допускающей монтажное ИЛИ(И) с открытым коллектором или с третьим состоянием, что целесообразней.

По этой причине все микроросхемы памяти выпускаются с такими выходами.

Похожие статьи

-

Устройство передающее сигнал с информационного входа на один из выходов, причем номер этого выхода равен десятичному эквиваленту двоичного кода на...

-

ОЗУ ДИНАМИЧЕСКОГО ТИПА - Цифровые устройства и микропроцессоры

В отличие от статических ЗУ, которые хранят информацию пока включено питание, в динамических ЗУ необходима постоянная регенерация информации, однако при...

-

ОЗУ СТАТИЧЕСКОГО ТИПА - Цифровые устройства и микропроцессоры

В качестве элемента памяти используется простейший D-триггер защелка. В микросхеме 537РУ10 каждая ЯП состоит из восьми триггеров и располагаются ячейки...

-

РЕГИСТРЫ, ПАРАЛЛЕЛЬНЫЕ И ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ - Цифровые устройства и микропроцессоры

Последовательностныесхемысразличнымикомбинациямипоследовательногои параллельного способов записи и считывания информации. Выполняются на основе...

-

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ - Цифровые устройства и микропроцессоры

Полупроводниковая память имеет большое число характеристик и параметров, которые необходимо учитывать при проектировании систем: 1. Емкость памяти...

-

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПАМЯТЬ) - Цифровые устройства и микропроцессоры

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и...

-

ТРИСТАБИЛЬНЫЕ ЭЛЕМЕНТЫ - Цифровые устройства и микропроцессоры

Наряду с двумя логическими состояниями существует третье технологическое состояние, когда выход элемента отключается от внутренней схемы. При этом...

-

СХЕМА КОНТРОЛЯ ЧЕТНОСТИ (НЕЧЕТНОСТИ) - Цифровые устройства и микропроцессоры

Схема применяется для выявления одиночных ошибок, вызванных помехами в линии связи или в блоках памяти. Метод основан на подсчете числа единиц в...

-

Микросхемы РПЗУ допускают многократное, до сотен тысяч, циклов перепрограммирования на рабочем месте пользователя. Это свойство обеспечивается...

-

ШИННЫЕ ФОРМИРОВАТЕЛИ - Цифровые устройства и микропроцессоры

В каждый момент времени на внутренней магистрали МПС допускается только один активный модуль, в распоряжении которого отдаются все ресурсы магистрали. В...

-

МУЛЬТИПЛЕКСОР - Цифровые устройства и микропроцессоры

Мультиплексор передает сигнал с одного из информационных входов xi на единственный выход y, причем номер этого входа равен десятичному эквиваленту...

-

Вариант № 6 Необходимо разработать цифровое комбинационное устройство демультиплексор из 1 в 4 в базисе ИЛИ-НЕ, НЕ, логическая функция которого указана...

-

Для n-логических переменных (аргументов) существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции...

-

СЧЕТЧИКИ - Цифровые устройства и микропроцессоры

Счетчик (Сч) - последовательностная схема, преобразующая поступающие на вход импульсы в код Q, пропорциональный их количеству. Большинство счетчиков...

-

ШИФРАТОР - Цифровые устройства и микропроцессоры

Шифратор (Ш) может быть неприоритетным, если допускается подача только одного активного сигнала и может быть приоритетным, если допускается подача...

-

T - ТРИГГЕР, ВЗАИМНЫЕ ПРЕОБРАЗОВАНИЯ ТРИГГЕРОВ - Цифровые устройства и микропроцессоры

Анализ временной диаграммы при J = K = 1 (рис. 46) позволяет сделать два важных вывода. Во-первых, период повторения выходных импульсов увеличился в два...

-

D - ТРИГГЕР СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ - Цифровые устройства и микропроцессоры

D - триггер имеет два входа: информационный вход D(аtа) и вход управления записью/запоминанием (защелкиванием) L(oad)/L(atch) - отсюда его второе имя :...

-

СИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Если незадействованные входы элементов И-НЕ 1 и 2 соединить вместе (рис. 36), получится синхронный RS - триггер со статическим управлением...

-

В таблице приведены усредненные типовые значениянекоторых параметров микросхем, выполненных по различным технологиям. В различных справочникахприведенные...

-

ПРИМЕНЕНИЕ ЦИФРОВЫХ УСТРОЙСТВ, ПЕРЕДАТОЧНАЯ ХАРАКТЕРИСТИКА - Цифровые устройства и микропроцессоры

ПЕРЕДАТОЧНАЯ ХАРАКТЕРИСТИКА В зависимости от схемотехники и технологии основного (базового) логического элемента (ЛЭ) существует несколько типов...

-

КОМБИНАЦИОННЫЕ СХЕМЫ, ДЕШИФРАТОР - Цифровые устройства и микропроцессоры

В комбинационных схемах логическая функция зависит только от комбинации значений входных переменных. При описании многих цифровых устройств невозможно...

-

Служит для отображения образа BCD или HEX цифры высвечиваемой на индикаторе в виде набора 0 и 1. Может быть принято следующее соответствие между битами и...

-

В данной работе разрабатывается микропроцессорная система минимальной конфигурацией, что предполагает использование управляющих сигналов, формируемых...

-

ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД, БУКВЕННО-ЦИФРОВОЙ КОД - Цифровые устройства и микропроцессоры

Двоично-десятичный код (ДДК) или Binary Coded Decimal (BCD) может быть упакованным, когда в одном байте хранятся две десятичные цифры, либо неупакованным...

-

Логический элемент И-НЕ с открытым коллектором (ОК) (см. рис.2. слева) обозначается в поле элемента ромбом с чертой внизу. К открытому коллектору снаружи...

-

АЦП ПАРАЛЛЕЛЬНОГО ТИПА - Цифровые устройства и микропроцессоры

В таком АЦП весь диапазон входного напряжения разбивается на 2^n интервалов. Каждому интервалу соответствует опорное напряжение Uо(i), снимаемое с...

-

ПРИМЕНЕНИЕ СЧЕТЧИКОВ В ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ - Цифровые устройства и микропроцессоры

На рисунке внизу последовательно включены 6 счетчиков с модулем 10 (двоично - десятичные). Информационные выходы Qi каждого каскада через преобразователь...

-

КАСКАДНОЕ ВКЛЮЧЕНИЕ СЧЕТЧИКОВ, СЧЕТЧИК - ТАЙМЕР - Цифровые устройства и микропроцессоры

Рассмотрим последовательное включение n - счетчиков с различными модулями счета Mi. Возможна постановка двух задач. В первой необходимо определить...

-

РЕВЕРСИВНЫЙ СЧЕТЧИК - Цифровые устройства и микропроцессоры

Схема двухразрядного счетчика с общим входом сброса R, выходом переноса CR при суммировании и выходом переноса BR при вычитании приведена на рис. внизу....

-

ПРОГРАММИРУЕМЫЕ ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ - Цифровые устройства и микропроцессоры

Проектирование современных цифровых устройств невозможно без использования программируемых цифровых ИС (ПЦИС). Они обладают следующими преимуществами...

-

СИНХРОННЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В синхронном счетчике импульсы поступают на тактовые входы всех триггеров одновременно. Ниже на рисунке ниже приведен трехразрядный счетчик с модулем...

-

АСИНХРОННЫЙ СЧЕТЧИК C ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В качестве примера возьмем четырехразрядный счетчик. Четыре двоичных разряда счетчика обеспечивают М = 16 состояний. Ниже приведена схема и условное...

-

АСИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Асинхронный триггер имеет два входа S(et) - установка и R(eset) - сброс и два выхода прямой - Q и инверсный - ~Q. Триггер переходит из текущего состояния...

-

ЛОГИЧЕСКИЙ БАЗИС, СХЕМНЫЕ ОСОБЕННОСТИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ - Цифровые устройства и микропроцессоры

Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Функции И, ИЛИ, НЕ не являются минимальным ЛБ, т....

-

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти...

-

Отличается от cтатического D-триггера свойствами L(C) входа. Запись информации происходит только в момент перехода тактового сигнала L из 0 в 1. При...

-

СУММАТОРЫ - Цифровые устройства и микропроцессоры

Сумматор осуществляет арифметическое суммирование n-разрядных кодов X=(x(n-1),..,x0) и Y=(y(n- 1),..,y0). Правила сложения двух одноразрядных двоичных...

-

СПОСОБЫ ПРЕДСТАВЛЕНИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ - Цифровые устройства и микропроцессоры

Целью проектирования цифрового устройства является получение его логической функции (ЛФ) и соответствующей ей схемной реализации. ЛФ могут иметь...

-

Микропроцессоры обрабатывают упорядоченные двоичные наборы. Минимальной единицей информации является один бит. Далее следуют - тетрада (4 бита), байт (...

-

Анализ работы устройства - Проектирование печатной платы программатора микросхем ПЗУ

Формирователь сигналов IBM представляет собой шинный формирователь, который пропускает сигналы с шины данных IBM (выходные сигналы регистра данных...

ЭНЕРГОНЕЗАВИСИМАЯ ПАМЯТЬ (NVSRAM), УВЕЛИЧЕНИЕ РАЗРЯДНОСТИ ЯЧЕЙКИ ПАМЯТИ (СЛОВА), УВЕЛИЧЕНИЕ КОЛИЧЕСТВА ЯЧЕЕК ПАМЯТИ - Цифровые устройства и микропроцессоры