ОЗУ СТАТИЧЕСКОГО ТИПА - Цифровые устройства и микропроцессоры

В качестве элемента памяти используется простейший D-триггер защелка. В микросхеме 537РУ10 каждая ЯП состоит из восьми триггеров и располагаются ячейки на кристалле в виде прямоугольной матрицы.

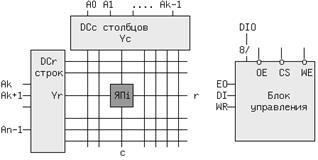

На рисунке приведены обозначения: n-адресных входов (A0 .. An-1), DIO - двунаправленная восмиразрядная шина данных, вход разрешения выходов - ~OE, вход выбора микросхемы - ~CS и вход разрешения записи - ~WE, который часто обозначают по другому - ~WR/RD, подчеркивая этим, что при низком значении сигнала на этом входе производится запись байта, а при высоком уровне - чтение. EO, DI, WR - внутренние сигналы вырабатываемые блоком управления чтением/записью/хранением. Доступ к произвольной ЯПj производится с помощью прямоугольного дешифратора, состоящего из двух обычных дешифраторов, причем k-адресных линий заводится на дешифратор столбцов (DCc), а оставшиеся n-k линий подключены к дешифратору строк (DCr). Количество строк и столбцов будет соответственно равно 2n-k и 2k, т. е. общее количество, обслуживаемых ЯП, равно 2k * 2n-k = 2n.

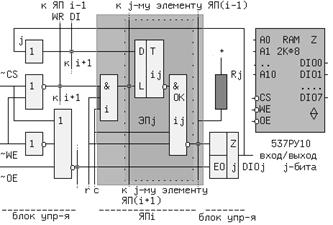

На рисунке внизу показан фрагмент внутренней структуры микросхемы, по которому можно проследить основные режимы ее работы. Здесь же дано условное обозначение микросхемы.

На рисунке схемы с открытым коллектором и третьим состоянием обозначены ОК и Z - соответственно. Точками выделен один (j-ый) из восьми элементов i-ой ячейки памяти. Схема И с номером i = (r * 2k + c) является одним из 2n выходных узлов прямоугольного дешифратора, где r и c - номера строк и столбцов матрицы. Инверсный вход (C)hip (S)elect - ~CS, во всех микросхемах, где он встречается, служит для приведения схемы в рабочее состояние низким уровнем сигнала на этом входе.

Если ~CS = 1 (пассивный уровень), микросхема - не выбрана и операции с ней производить невозможно. Из рис. видно, что в этом случае на L-входе D-триггера - ноль, запись невозможна и триггер хранит ранее записанный бит. Прочитать выходной код - Q тоже нельзя, т. к. на прямом входе EO разрешения выхода запрещающий нулевой сигнал и вход/выход DIOi находится в третьем состоянии.

С поступлением ~CS = 0, схемы ИЛИ-НЕ разблокируются и дальше все зависит от значений сигналов ~WE и ~OE.

В режиме записи сигнал ~WE = 0. Поэтому независимо от значения сигнала ~OE на входе схемы, внутренний сигнал EO, тоже равен 0, и чтение данных во время записи невозможно. На верхнем входе элемента Иi - единица и, если на адресных входах код An-1,An-2,...,A1,A0(BIN) = i(DEC), то сигналы на линиях Yr и Yc тоже равны 1 и триггер ij прозрачен для записи входной информации DIOj.

В режиме чтения ~WE=1, ~OE=0 и при Yr=Yc=1, выходной сигнал ~Q после инверсии элементом Иij с открытым коллектором проходит на выход DIOi.

Следует обратить внимание на то, что выходы всех 2^n j-ых элементов памяти должны подключаться к общему j-му выводу микросхемы - DIOj. Такое объединение выходов возможно с помощью схемного либо монтажного И(ИЛИ). Монтажное И(ИЛИ) не требует дополнительных схем и может выполняться на элементах с открытым коллектором или с третьим состоянием. Внутри рассматриваемой схемы j-е выходы

ЭП объединены на общем резисторе Rj, служащем нагрузкой элементов И-НЕij с открытым коллектором.

Для увеличения информационной емкости, отдельные микросхемы группируются в банки и их одноименные выходы должны объединяться. По этой причине выходы всех микросхем памяти также выполняются с открытым коллектором либо с третьим состоянием.

В ЭВМ статическое ОЗУ используется в быстродействующей Cash-памяти.

Похожие статьи

-

ТРИСТАБИЛЬНЫЕ ЭЛЕМЕНТЫ - Цифровые устройства и микропроцессоры

Наряду с двумя логическими состояниями существует третье технологическое состояние, когда выход элемента отключается от внутренней схемы. При этом...

-

СИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Если незадействованные входы элементов И-НЕ 1 и 2 соединить вместе (рис. 36), получится синхронный RS - триггер со статическим управлением...

-

МУЛЬТИПЛЕКСОР - Цифровые устройства и микропроцессоры

Мультиплексор передает сигнал с одного из информационных входов xi на единственный выход y, причем номер этого входа равен десятичному эквиваленту...

-

Помимо аналого-цифровых преобразователей (АЦП), работой цифровой логики могут управлять операционные усилители (ОУ) и компараторы, преобразующие...

-

Всякая память сохраняющая данные при отключении внешнего источника питания может считаться энергонезависимой - NonVolatile Memory, однако этот термин...

-

РЕГИСТРЫ, ПАРАЛЛЕЛЬНЫЕ И ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ - Цифровые устройства и микропроцессоры

Последовательностныесхемысразличнымикомбинациямипоследовательногои параллельного способов записи и считывания информации. Выполняются на основе...

-

D - ТРИГГЕР СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ - Цифровые устройства и микропроцессоры

D - триггер имеет два входа: информационный вход D(аtа) и вход управления записью/запоминанием (защелкиванием) L(oad)/L(atch) - отсюда его второе имя :...

-

Вариант № 6 Необходимо разработать цифровое комбинационное устройство демультиплексор из 1 в 4 в базисе ИЛИ-НЕ, НЕ, логическая функция которого указана...

-

АСИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Асинхронный триггер имеет два входа S(et) - установка и R(eset) - сброс и два выхода прямой - Q и инверсный - ~Q. Триггер переходит из текущего состояния...

-

Логический элемент И-НЕ с открытым коллектором (ОК) (см. рис.2. слева) обозначается в поле элемента ромбом с чертой внизу. К открытому коллектору снаружи...

-

ОЗУ ДИНАМИЧЕСКОГО ТИПА - Цифровые устройства и микропроцессоры

В отличие от статических ЗУ, которые хранят информацию пока включено питание, в динамических ЗУ необходима постоянная регенерация информации, однако при...

-

Устройство передающее сигнал с информационного входа на один из выходов, причем номер этого выхода равен десятичному эквиваленту двоичного кода на...

-

КОМБИНАЦИОННЫЕ СХЕМЫ, ДЕШИФРАТОР - Цифровые устройства и микропроцессоры

В комбинационных схемах логическая функция зависит только от комбинации значений входных переменных. При описании многих цифровых устройств невозможно...

-

ЛОГИЧЕСКИЙ БАЗИС, СХЕМНЫЕ ОСОБЕННОСТИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ - Цифровые устройства и микропроцессоры

Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Функции И, ИЛИ, НЕ не являются минимальным ЛБ, т....

-

Расчет схемы электрической принципиальной цифрового матрицирующего устройства. Рассмотрим систему обозначений сигналов, принятую в цифровом телевидении...

-

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ СХЕМЫ, ТРИГГЕРЫ - Цифровые устройства и микропроцессоры

В последовательностных схемах (ПС) выходные сигналы зависят не только от комбинаций входных, но и от значений самих выходных сигналов в предшествующий...

-

АСИНХРОННЫЙ СЧЕТЧИК C ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В качестве примера возьмем четырехразрядный счетчик. Четыре двоичных разряда счетчика обеспечивают М = 16 состояний. Ниже приведена схема и условное...

-

РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА - Цифровые устройства и микропроцессоры

Название указывает, что сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую. Одна из возможных схем трехразрядного...

-

СУММАТОРЫ - Цифровые устройства и микропроцессоры

Сумматор осуществляет арифметическое суммирование n-разрядных кодов X=(x(n-1),..,x0) и Y=(y(n- 1),..,y0). Правила сложения двух одноразрядных двоичных...

-

В таблице приведены усредненные типовые значениянекоторых параметров микросхем, выполненных по различным технологиям. В различных справочникахприведенные...

-

ПРОГРАММИРУЕМЫЕ ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ - Цифровые устройства и микропроцессоры

Проектирование современных цифровых устройств невозможно без использования программируемых цифровых ИС (ПЦИС). Они обладают следующими преимуществами...

-

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти...

-

Микросхемы РПЗУ допускают многократное, до сотен тысяч, циклов перепрограммирования на рабочем месте пользователя. Это свойство обеспечивается...

-

Применяя к выражению (13) аксиому двойного отрицания (9) получим: Yмажор =~(~( x2*x0 + x1*x0 + x2*x1))(14) Формуле (14) соответствует схема (рис.8,слева)...

-

СИНХРОННЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В синхронном счетчике импульсы поступают на тактовые входы всех триггеров одновременно. Ниже на рисунке ниже приведен трехразрядный счетчик с модулем...

-

Цифровые устройства и микропроцессоры

Введение Счетчики выполняют на запоминающих элементах - триггерах. Он фиксирует число импульсов, поступивших на его вход. В интервалах между ними счетчик...

-

СЧЕТЧИКИ - Цифровые устройства и микропроцессоры

Счетчик (Сч) - последовательностная схема, преобразующая поступающие на вход импульсы в код Q, пропорциональный их количеству. Большинство счетчиков...

-

T - ТРИГГЕР, ВЗАИМНЫЕ ПРЕОБРАЗОВАНИЯ ТРИГГЕРОВ - Цифровые устройства и микропроцессоры

Анализ временной диаграммы при J = K = 1 (рис. 46) позволяет сделать два важных вывода. Во-первых, период повторения выходных импульсов увеличился в два...

-

АЦП ПАРАЛЛЕЛЬНОГО ТИПА - Цифровые устройства и микропроцессоры

В таком АЦП весь диапазон входного напряжения разбивается на 2^n интервалов. Каждому интервалу соответствует опорное напряжение Uо(i), снимаемое с...

-

ЦАП И АЦП, ЦАП С МАТРИЦЕЙ РЕЗИСТОРОВ R-2R - Цифровые устройства и микропроцессоры

Цифроаналоговые преобразователи (ЦАП) численные данные преобразуют в аналоговый сигнал, Чаще в напряжение или в ток и служат для связи цифровых и...

-

ПРИМЕНЕНИЕ СЧЕТЧИКОВ В ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ - Цифровые устройства и микропроцессоры

На рисунке внизу последовательно включены 6 счетчиков с модулем 10 (двоично - десятичные). Информационные выходы Qi каждого каскада через преобразователь...

-

РЕВЕРСИВНЫЙ СЧЕТЧИК - Цифровые устройства и микропроцессоры

Схема двухразрядного счетчика с общим входом сброса R, выходом переноса CR при суммировании и выходом переноса BR при вычитании приведена на рис. внизу....

-

Программируемыепостоянныезапоминающиеустройства(ППЗУ)делятсянаоднократно программируемые (например, биполярные ПЗУ с плавкими соединениями) и...

-

Отличается от cтатического D-триггера свойствами L(C) входа. Запись информации происходит только в момент перехода тактового сигнала L из 0 в 1. При...

-

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПАМЯТЬ) - Цифровые устройства и микропроцессоры

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и...

-

ШИННЫЕ ФОРМИРОВАТЕЛИ - Цифровые устройства и микропроцессоры

В каждый момент времени на внутренней магистрали МПС допускается только один активный модуль, в распоряжении которого отдаются все ресурсы магистрали. В...

-

Для n-логических переменных (аргументов) существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции...

-

ОПРЕДЕЛЕНИЯ НЕКОТОРЫХ ПАРАМЕТРОВ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ - Цифровые устройства и микропроцессоры

Ниже приведены некоторые параметры в отечественном по ГОСТ 19480-89 и международном обозначении. Tзд. р.1,0 / tPHL - время задержки распространения при...

-

СХЕМА КОНТРОЛЯ ЧЕТНОСТИ (НЕЧЕТНОСТИ) - Цифровые устройства и микропроцессоры

Схема применяется для выявления одиночных ошибок, вызванных помехами в линии связи или в блоках памяти. Метод основан на подсчете числа единиц в...

-

КАСКАДНОЕ ВКЛЮЧЕНИЕ СЧЕТЧИКОВ, СЧЕТЧИК - ТАЙМЕР - Цифровые устройства и микропроцессоры

Рассмотрим последовательное включение n - счетчиков с различными модулями счета Mi. Возможна постановка двух задач. В первой необходимо определить...

ОЗУ СТАТИЧЕСКОГО ТИПА - Цифровые устройства и микропроцессоры