Вибір елементної бази пристрою, Розробка схеми електричної принципової пристрою - Розробка блоку зв'язку з електроавтоматикою верстата 16Б16. Пристрій управління шпінделем

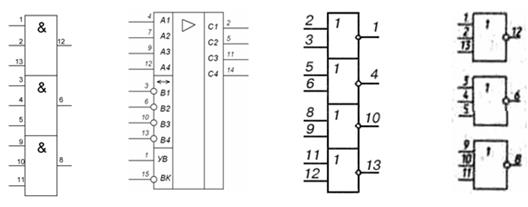

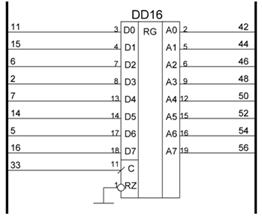

Для шинних формувачів вибираємо 4 мікросхеми К589АП26. Вхідний вузол формуємо на мікросхемах КР1533ЛЕ1 - 4 незалежних елементи "2 ИЛИ-НЕ". Сигнал ВБ (вибір банку) формуємо на мікросхемах КР1533ЛИ3 - 3 елементи "3И", КР155ЛЕ4 - 3 елементи "3ИЛИ-НЕ", КР1533ЛЕ1 - 4 елементи "2ИЛИ-НЕ", КР1533ЛИ1 - 4 елементи "2И". Сигнали РС та РД реалізовуємо на мікросхемах КР1533ЛН1 - 6 елементів "ИЛИ-НЕ", КР1533ЛИ1 - 4 елементи "2И", КР1533ЛИ3 - 3 елементи "3И", К155ЛЕ3 - 2 елементи "4ИЛИ-НЕ", КР1533ЛИ1 - 4 елементи "2И". Регістр адреси реалізовуємо на тригерах К555ТМ2- це здвоєний двухрозрядний тригер. Регістр даних будуємо на мікросхемі КР1533ИР22- це восьмирозрядний регістр. Також використовуємо мікросхему КР1533КП7- це мультиплексор. К1533КП7 - селектор - мультиплексор на 8 каналів зі стробуванням. КР155ЛА3 - 4 логічні елементи "2И-НЕ", К555ЛЛ1 - 4 логічних елемента "2ИЛИ" (Рисунок 2).

Рисунок 2

Рисунок 3

Рисунок 4 - Логічні елементи

Розробка схеми електричної принципової пристрою

Розробка інтерфейсної частини блоку

Вихідні дані: адреси блоку - 160636, 160640; напруга живлення логічного блоку - 5В; напруга живлення зовнішніх пристроїв - 24 В; індикація станів схеми; розв'язання дискретних входів і виходів.

Згідно вихідних даних розробляємо інтерфейсну частину блоку:

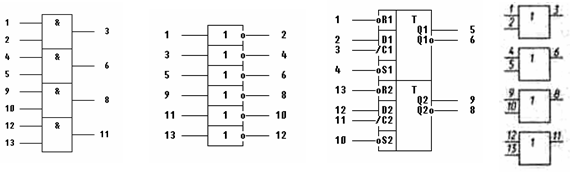

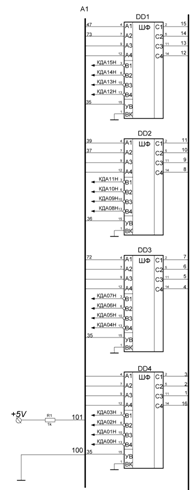

Розробка шинних формувачів. Центральний процесор формує на лініях КДА (00-15) Н адрес. Адрес надходить на шинні формувачі DD1-DD4, виконані на чотирьох мікросхемах К589АП26 (Рисунок 5).

Рисунок 5 - Схема електрична принципова шинних формувачів

Далі проаналізуємо рівень сигналу УВ - управляючий вихід, призначений для управління напрямом передачі даних. Якщо УВ=1, передача виконується з порта В до порта С. Якщо УВ=0, передача виконується від порта А до порта В шинних формувачів. Для аналізу рівня сигнала УВ розглянемо вузол прийому вхідних сигналів управління (Рисунок 6):

Рисунок 6 - Схема електрична вхідного вузла

Розробляємо селектор адреси. Для цього треба виділити адресу блоку - 160636, 160640, та розкласти її у двійковій системі (Таблиця 1):

Таблиця 1 - Таблиця ваги розрядів

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 | |

|

160636 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

160640 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

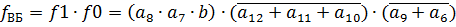

Згідно таблиці, розряди 15,14,13 є сигналами високого рівня, тому можна замінити ці розряди одним спільним сигналом ВУВ, позначимо його b. Крім того при звернені до блоку сигнали розрядів 8 і 7 мають високий рівень. Сигнали високого рівня формують функцію f1:

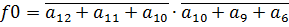

Розряди 12,11,10,9 і 6 мають низький рівень сигналу і формують функцію f0:

Функція вибір банку (fВБ) звернення до блоку здійснюється за парними адресами, тому 0-ий розряд можна не враховувати:

Рисунок 7 - Схема електрична принципова формування сигналу ВБ

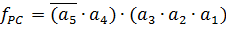

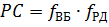

Функція звернення до регістру стану (PC) повинна формуватися тільки в випадку звернення за адресою 160636:

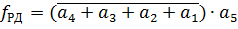

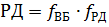

Функція звернення до регістру даних (РД) повинна формуватися тільки в випадку звернення за адресою 160640:

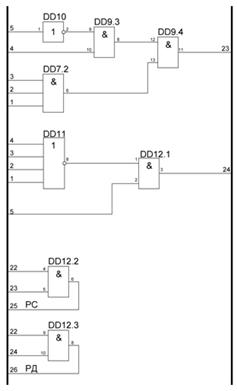

Рисунок 8 - Схема електрична принципова формування сигналів РС і РД

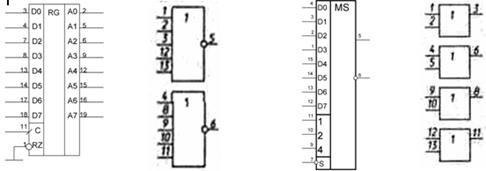

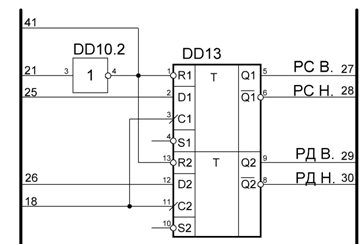

Розробляємо регістр адреси. Регістр адреси призначений для запам'ятовування адреси за якою звертається центральний процесор. Виконуємо регістр адреси на тригерах серії К555ТМ2, які вміщують в себе два D-тригера. Подаємо на входи тригера сигнал РС і РД і отримуємо вже сформовані та збережені сигнали завдяки сигналу СІА.

Рисунок 9 - Схема електрична принципова регістра адреси

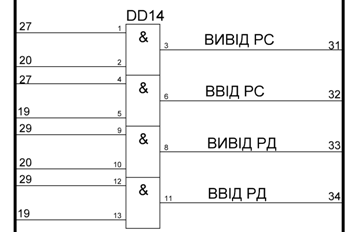

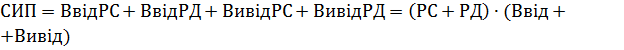

Розробляємо формувач сигналів управління. Сигнали управління записом або зчитуванням інформації формуються при обов'язковій наявності двох сигналів Вивід або Ввід та РД або РС:

Рисунок 10 - Схема електрична принципова формувача сигналів зчитування в РС та РД

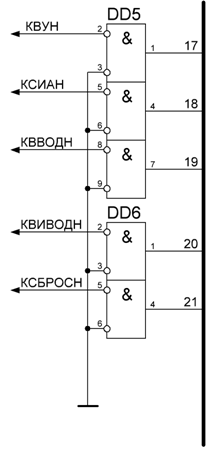

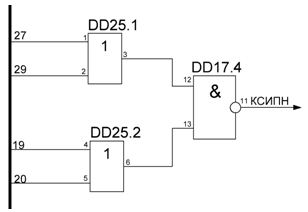

Сигнал відповіді блоку - КСИПН, формується при наявності одного із сигналів управління:

Рисунок 11 - Схема електрична принципова формувача сигналу КСИПН

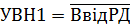

Вузол формування сигналів перемикання шинних формувачів (УВН) при зчитуванні інформації з РС та РД:

Рисунок 12 - Схема електрична принципова формувача сигналу УВН

Розробляємо регістр даних і регістр стану. Це вузол блоку, котрий повинен за сигналом ВИВІД РД запам'ятовувати 8 ліній сигналів, що надходить від шинного формувача, що і сформує дозволяючий сигнал на регістри, після чого дані направляться на вихід регістрів на функції. Входи регістра даних формують вхідні сигнали для функціональних вузлів (по 4 сигнали на кожний вузол ) (Рисунок 13):

Рисунок 13 - Схема електрична принципова регістру даних

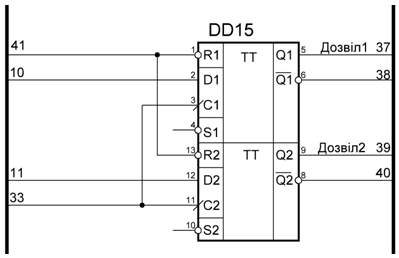

Регістр стану ( РС) формує сигнали Дозвіл 1 і Дозвіл 2 за допомогою яких вихідні функції або видаються на верстат або їхня видача забороняється (Рисунок 14).

Рисунок 14 - Схема електрична принципова регістру стану

Похожие статьи

-

Робота блоку розпочинається з того, що центральний процесор формує на лініях КДА00-15Н адрес, він надходить на шинні формувачі (ШФ), і при цьому...

-

Робота блоку розпочинається з того, що центральний процесор формує на лініях КДА00-15Н адрес, він надходить на шинні формувачі (DD1-DD4), і при цьому...

-

За вихідними даними нам потрібно реалізувати: формувач сигналу, що реалізує функцію 4-х вхідних сигналів за ознакою більшості; формувач сигналів Fx та...

-

Вихідні дані: адреси блоку - 160636, 160640; напруга живлення логічного блоку - 5В; напруга живлення зовнішніх пристроїв - 24 В; індикація станів схеми;...

-

Вимірювач частота сигнал потужність Пристрій повинен складатися зі зовнішнього пульта, який під'єднується до паралельного порта ПЕОМ. Пульт повинен мати...

-

Щоб визначити загальну потужність, що споживається нашим блоком, потрібно спочатку визначити потужність, що споживають мікросхеми. Занесемо всі...

-

Вступ - Розробка блоку зв'язку з електроавтоматикою верстата 16Б16. Пристрій управління шпінделем

Числове програмне керування (ЧПК) (англ. Computer numerical control) - комп'ютеризована система керування, яка зчитує командні інструкції спеціалізованої...

-

Так як ми вже визначились зі структурною схемою приладу, то потрібно розробити електричну принципову. Спочатку визначимось з усіма складовими окремо. В...

-

Розробка функціональної схеми моноімпульсної РЛС Виходячи з послідовності операцій, які виконує моноімпульсни система, її функціональна схема повинна...

-

Опис принципової схеми Пульт керування Пульт керування кондиціонером містить два РКІ індикатора поточної температури приміщення і задається користувачем...

-

Пристрій може виявляти й декодувати сигнали малої амплітуди. Для досягнення цього DVDD, AVDD і VBIAS повинні бути розв'язані, а тракт прийому ?...

-

Розроблений пристрій призначений для проведення лабораторної роботи з предмету "Цифрова схемотехніка". Він дозволяє дослідити та наочно показати роботу...

-

Вибір елементної бази - Цифровий датчик тиску повітря у кабіні літака

Вибір процесорного модуля. Процесорний модуль призначений для прийому, збереження й обробки даних, а також видачі керуючих команд периферійним пристроям....

-

Зазвичай в РЛС сантиметрового діапазону у якості малошумлячого підсилювача МШП надвисоких частот НВЧ використовують тільки напівпровідниковий...

-

Для обгунтування власного технічного рішення робимо висновки з інформації наведеної в пункті 8. 1. Наявність в кондиціонері такої базової функції, як...

-

Опис вибору елементної бази та роботи принципової схеми - Автоматичний регулятор температури

Схема терморегулятора показана на рис.7 (Додаток В). Резистором R8 встановлюють необхідну контрастність зображення індикатора. Всі блоки пристрою...

-

У варіантах реалізації приладу, розглянутих у 1 розділі немає можливості задавати частоту вихідного сигналу, а тільки амплітуду, що не задовольняє умови...

-

Опис функціональної схеми модему - Захист інформації від витоку з телефонної мережі зв'язку

На рис. 7.2 представлена функціональна схема мікросхеми СМХ869, а в таблиці 7.1 наведено опис вхідних і вихідних сигналів. Рисунок 7.2 Функціональна...

-

Основний недолік аналогових РРЛ є те, що викривлення переданих по них сигналів, які виникають у процесі формування, перетворення, ущільнення і...

-

Вибір і обгрунтування елементної бази - Лабораторний стенд-мультиплексор (блок мультиплексування)

При проектуванні цифрових пристроїв однією з важливих задач є вибір елементів. Вибір елементної бази проводиться на основі схеми електричної принципової...

-

Необхідність подальшого удосконалення військових засобів РР зв'язку та їх основних частин На озброєнні в підрозділах і частинах ЗС МО України знаходиться...

-

Загальні положення П'єзоелектричними називають фільтри, що складаються з п'єзоелектричного резонатора, індуктивностей і ємностей. Застосовуються в...

-

Розрахуємо спочатку елементи клавіатури. В клавіатурі використовуються резистори R1, R3, R4, R5, R8, R10, R12, R15, R16, R18, R20, R21, R22, відповідно...

-

AT90S2313 - економічний 8 бітовий КМОН-мікроконтролер, побудований з використанням розширеної RISC архітектури AVR. Виконуючи по одній команді за період...

-

Рекомендації щодо використання вітчизняної елементної бази - Реалізації технології ЦДУ

Повнота реалізації переваг ЦАР багато в чому залежить від якісних параметрів елементної бази. Прогрес у розвитку мікропроцесорної техніки і теорії ЦОС...

-

Повністю схема функціональна подана у додатку. Нижче розписано основні аспекти стосовно розробки кожного окремого вузла. Розробка вузла синхронізації...

-

ОБГРУНТУВАННЯ ТА РОЗРОБКА СТРУКТУРНОЇ СХЕМИ ВИМІРЮВАЛЬНОГО ПРИЛАДУ - Цифровий вимірювач ваги

Для того, щоб визначитись із структурною схемою цифрового вимірювача ваги, необхідно вибрати первинний перетворювач, датчик ваги. Згідно індивідуального...

-

Выбор и обоснование схемы электрической структурной - Блок сопряжения телефонной связи

В данном дипломном проекте рассматривается схема блока сопряжения. Блок представляет собой устройство с двумя усилителями и кнопкой вызова внешнего...

-

З погляду виробників мікропроцесорної техніки всі задачі, вирішувані системами вбудованого управління, поділяються на два великі класи: управління...

-

Опис портів введення-виведення MS DOS може працювати з трьома паралельними пристроями (LPT1 - LPT3). Для підключення використовується стандартне...

-

Формирователь импульсов, Счетчик импульсов - Цифровой блок управления резьбонарезным шпинделем

В качестве ФИ используем триггер Шмитта, который позволяет исключить влияние помехи и повысить крутизну фронта среза импульсов подаваемых на СИ. Так как...

-

Термокомпенсація заданого фрагмента схеми ЕА В процесі вибору ЕБ для ЕА часто виникає потреба у забезпеченні температурної стабільності окремих ланцюгів...

-

Для налаштування антени булоб добре знати потужність сигналу на виході конвертора. Це можливо зробити знаючи ЕІВП супутника (карти зон покриття тим чи...

-

Проектирование схемы тактирования АЦП. - Разработка аналого-цифрового преобразователя

Схема тактирования предназначена для подачи тактовых импульсов, а также для подачи стартового импульса на регистр последовательных приближений. Схема...

-

Розробка принципової схеми вантажного району - Проектування залізничного вузла

Вантажний райони вантажних станцій по своєму технічному оснащенню не відрізняються від вантажних районів крупних дільничних станцій. На них...

-

Програмне забезпечення (ПЗ) є однією з важливих частин будь-якого обчислювального пристрою. Взагалі ПЗ являє собою сукупність програм, функціонально...

-

РРС Р-415 призначена для створення тимчасових швидкорозгортаємих малоканальних радіорелейних ліній зв'язку, а також для відгалуження каналів від...

-

Критерієм оптимальності однієї з прийнятих до розгляду варіантів схем електричних з'єднань, в порівнянні з іншими варіантами схем, за умови дотримання...

-

Роз'єднання туго посаджених деталей представляє значні труднощі, і крім того при цьому можна пошкодити роз'єднувальні деталі. Щоб при розбиранні не...

-

До приймачів РЛС пред'являються жорсткіші вимоги, ніж до приймачів іншого призначення. Багато РЛС є частиною стратегічних комплексів виявлення об'єктів....

Вибір елементної бази пристрою, Розробка схеми електричної принципової пристрою - Розробка блоку зв'язку з електроавтоматикою верстата 16Б16. Пристрій управління шпінделем