Проверка схемы и отображение ошибок - Проект печатных плат электронных устройств в системе автоматизированного проектирования P-CAD

Созданная схема в редакторе Schematic должна быть проверена на наличие ошибок, так как при наличии таковых проектирование ПП не может быть произведено. После устранения недостатков можно приступать к проектированию ПП.

Для отображения ошибок на схеме в опциях дисплея (Options Display) на вкладке Miscellaneous (Разное) в группе ERC Errors устанавливается режим отображения выявленных ошибок схемы. При выборе переключателя Show (Показать) обнаруженные ошибки указываются на схеме специальным индикатором.

В поле ввода Size (Размер) этой группы можно задать размер индикатора ошибки, который может варьироваться в пределах от 0.025 до 10 мм.

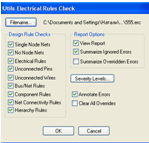

Проверка схемы на ошибки осуществляется по команде Utils | ERC (Electrical Rules Check). В меню данной команды задается перечень проверок, результаты которых приводятся в текстовом отчете.

Рисунок 7 - Настройка конфигурации ERC

Список проверяемых ошибок приведен в таблице 2.

Таблица 2 Правила проверки схем

|

Правило проверки |

Что проверяется |

|

Single Node Nets |

Цепи, имеющие единственный узел |

|

No Node Nets |

Цепи, не имеющие узлов |

|

Electrical Rules |

Электрические ошибки, когда соединяются выводы несовместимых типов, например, выход логической микросхемы подключается к источнику питания |

|

Unconnected Pins |

Неподключенные выводы символов |

|

Unconnected Wires |

Неподключенные сегменты цепей |

|

Bus/Net Rules |

Входящие в состав шины цепи встречаются только один раз или к шине не подходит ни одного провода |

Для просмотра отчета об ошибках необходимо включить опцию View Report (просмотр отчета), для индикации ошибок на схеме - Annotate Errors. Приоритет ошибок устанавливается в окне Severity Levels (Ранжирование ошибок):

- - Errors - ошибка; - Warning - предупреждение; - Ignored - игнорирование ошибки.

После ввода необходимой конфигурации при нажатии ОК создается отчет об ошибках и заносится в файл с расширением *.erc.

2.5 Генерация списка соединений

Важным этапом работы со схемой является получение списка соединения компонентов, который может быть использован в редакторе печатных плат для трассировки проводников. Список соединений включает в себя список компонентов и цепей с указанием номеров выводов компонентов, к которым они подключены. Данный список используется для так называемой процедуры "упаковки схемы на печатную плату" - размещения на поле печатной платы корпусов компонентов с указанием их электрических связей согласно принципиальной схеме.

Для создания списка в меню Utils необходимо выбрать Generate Netlist (Генерация соединений) (рисунок 8).

Рисунок 8 - Выбор формата списка соединений

В данном окне в списке Netlist Format (формат списка соединений) выбирается формат списка соединений: P-CAD ASCII, Tango, FutureNet Netlist, FutureNet Pinlist, Master Design, Edif 2.0.0, PSpice, XSpice. Для разработки ПП с помощью графического редактора PCB выбирается формат P-CAD ASCII. Нажав кнопку Netlist Filename (Имя файла списка цепей), необходимо выбрать файл списка соединений. Активация функции Include Library Information позволяет включить в файл списка соединений (только для формата P-CAD ASCII) информацию необходимую для составления с помощью Library Manager библиотеки символов компонентов, находящихся в данном проекте (по команде Library | Translate). Для разработки печатной платы данная информация не используется.

Похожие статьи

-

Целью работы является проектирование с помощью программного продукта P-CAD 2004 печатных плат четырех электронных устройств, в том числе печатной платы...

-

При работе над проектом разрабатывались два основных компонента системы: база данных (далее - БД) и интерфейс клиентского приложения. Затем необходимо...

-

После разработки рисунка ПП его необходимо проверить на соответствие исходной принципиальной схеме и соблюдение технологических ограничений. Для это...

-

Создание любого электронного устройства включает в себя следующие этапы: - Формирование технического задания (ТЗ) на разработку, определение структуры и...

-

Важнейшим вопросом при создании САПР после формализации процесса проектирования является вопрос отображения проектно-конструкторской деятельности...

-

Топология ПП представляет собой наглядное изображение проектируемой платы. Топология ПП включает: границы ПП, корпуса РЭК с посадочными местами,...

-

Создание принципиальной схемы в P-CAD осуществляется в схемном редакторе Schematic. Окно данного редактора показано на рисунке 1. Основными элементами...

-

Описание принципиальной электрической схемы Проектируемый модуль логический используется в системе управления цикловыми промышленными роботами. Он...

-

Осуществить компоновку элементов схемы можно как вручную, так и автоматически. Для запуска автоматического позиционирования элементов необходимо...

-

Принципиальная электрическая схема определяет полный состав элементов и связей между ними и дает детальное представление о принципах работы объекта...

-

DipTrace имеет интегрированные библиотеки, которые содержат графическую информацию о символах и типовых корпусах компонентов и текстовую упаковочную...

-

Выбранные датчики, исполнительные механизмы и их месторасположение, а также структурная схема АСУ ТП производства сухого молока позволяют составить схему...

-

Физическая модель базы данных определяет способ размещения данных в среде хранения и способ доступа к этим данным, которые поддерживаются на физическом...

-

Специфика информационного обеспечения САПР - Состав систем автоматизированного проектирования

В комплекс средств автоматизированного проектирования входит информационное обеспечение, которое представляет собой совокупность документов, описывающих...

-

Перед началом непосредственного использования программы "Сервер опроса", следует создать рабочую конфигурацию сервера с помощью программы - конфигуратора...

-

Программирование В соответствии со структурной схемой приложения (п.4.1.2), разработаны программные модули на языке Delphi 7. Кроме того разработаны...

-

Общие сведения о тестировании Данный раздел посвящен проведению тестирования клиентского приложения. Тестирование для серверной части системы не...

-

Сам датчик поставляется в трех видах корпусов, в 8-выводном SOIC-е, 8-выводном uSOP-е, и, пожалуй, самым популярном, ТО-92. Для связи с управляющей...

-

Работа со меню и списками Внешний вид списка Пример внешнего вида списка приведен на рисунке 7. Рисунок 7 -- Внешний вид списка. Каждый раздел Системы...

-

Введение - Проектирование платы устройства управления вентиляторами компьютера через порт

В настоящее время при проектировании радиоэлектронной аппаратуры важную роль приобретает использование систем автоматизированного проектирования (САПР)...

-

Отчет представляет собой полученный на принтере выходной документ, предназначенный для конечного пользователя. Отчет - наилучшее средство для...

-

В данном разделе была разработана функциональная схема работы программного комплекса, которая в общем виде описывает состав комплекса, характер и виды...

-

Возрастающая сложность современных автоматизированных систем управления и повышение требовательности к ним обуславливает применение эффективных...

-

Сетевая топология -- способ описания конфигурации сети, схема расположения и соединения сетевых устройств. Существует множество способов соединения...

-

Структурная схема АСУ ТП водоснабжения При разработке системы автоматизированного управления технологическим процессом водоснабжения необходимо...

-

Итак, для того чтобы построить устройство, нам нужно определиться, что мы будем использовать в качестве источника информации и куда будем передавать...

-

Расширенное техническое задание 1. Наименование изделия: устройство управления вентиляторами компьютера через порт LPT. 2. Назначения: устройство...

-

В связи с увеличением числа сотрудников, работающих в компании, а также с расширением рабочего проекта, возникла проблема, связанная с версионностью...

-

Первичные документы: Заявка от заказчика, наряд на выполнение работ, акт выполнения работ 1) Заявка от заказчика Рисунок 7. Дерево взаимосвязи реквизитов...

-

Функции CAD-систем в машиностроении подразделяют на функции двухмерного (2 D ) и трехмерного (3 D ) проектирования. К функциям 2 D Относятся черчение,...

-

Высокая плотность размещения элементов ЭВА создает большие трудности при реализации соединений между ними. В этой связи задача размещения элементов на...

-

В качестве предметной области для дипломного проекта была выбрана организация МКДОУ детский сад №85 "Почемучка". Описание и основные виды деятельности...

-

Данная глава посвящена описанию автоматизированного тестирования, его типам, выявлению достоинств и недостатков в автоматизации тестирования. Более того...

-

Все IP-адреса в автономных системах имеют "серый" адрес, то есть адрес, которым нельзя воспользоваться для выхода в Интернет (классы таких адресов были...

-

На основании примерного порядка рассмотрения проекта законодательной инициативы законодательного (представительного) органа государственной власти...

-

Широкое распространение в операционной системе Windows имеет множество стандартных программ обеспечивающих работу устройств компьютера и служащих для...

-

Если множество элементов объединено в систему по определенному признаку, то всегда можно ввести некоторые дополнительные признаки для разделения этого...

-

Если в результате поиска на схеме по данным из таблицы будет найдено несколько экземпляров оборудования (т. е. с одинаковой маркировкой или...

-

Системы, расположенные на материнской плате - Усовершенствование материнской платы

Процессор - основная микросхема компьютера, в которой и производятся все вычисления. Конструктивно процессор состоит из ячеек, похожих на ячейки...

-

ООО "Евротехноторг" - предприятие, которое занимается закупкой и реализацией рыбных консервов. Торговая деятельность сопровождается оформлением большого...

Проверка схемы и отображение ошибок - Проект печатных плат электронных устройств в системе автоматизированного проектирования P-CAD