РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ КОДЕКА - Разработка кодека сверточного кода с алгоритмом порогового декодирования

Критерием выбора принципа построения функциональных блоков кодека является обеспечение минимума сложности аппаратной реализации.

В соответствии с [1-3] задание порождающих полиномов и алгоритма декодирования ССК полностью определяет принцип построения функциональной схемы кодека.

Функциональная электрическая схема ФПСк (ФПСд) выполняется в виде схемы умножения полиномов, и реализуются в виде регистра сдвига (RG) со встроенными сумматорами по модулю два.

Так как максимальная степень порождающих полиномов, то RG будет содержать ячеек памяти и такое же количество сумматоров по модулю два.

Функциональная электрическая схема ФПСк (ФПСд) приведена на рисунок 4.1.

Рисунок 4.1 - Функциональная электрическая схема ФПСк (ФПСд)

Нумерация ячеек памяти RG ФПСк ведется справа налево. Места включения сумматоров по модулю два определяются ненулевыми членами порождающих полиномов. Выходной сумматор по модулю два является трех входовым.

Наиболее простым способом построения КРИ-1/2 является использование двух регистров (RG1, RG2) и блока формирования тактовых частот RG1 и RG2. Оба регистра содержат по ячеек памяти.

Способ построения КРИ-1/3 является аналогичным способу построения КРИ-1/2, различие заключается лишь в количестве ячеек памяти у регистров RG1 и RG2, а также в блоке формирования тактовых частот.

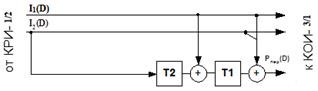

Функциональная электрическая схема КРИ-1/2 представлена на рисунке 4.2.

Рисунок 4.2 - Функциональная электрическая схема КРИ-1/2

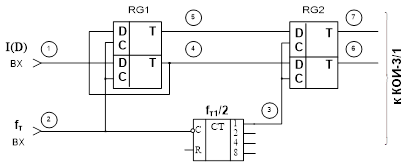

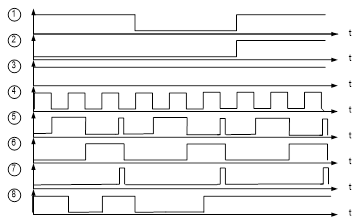

Диаграммы, поясняющие принцип работы КРИ-1/2, приведены на рисунке 4.3.

Рисунок 4.3 - Временные диаграммы, поясняющие принцип работы КРИ-1/2

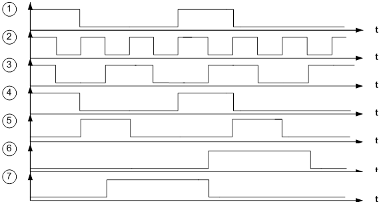

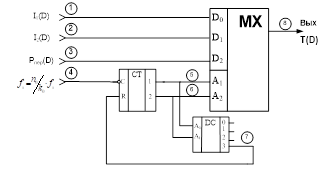

КОИ-3/1 и КОИ-2/1 соответственно кодера и декодера ССК целесообразно выполнить в виде синхронных мультиплексоров на соответствующее число информационных и управляющих входов, а также формирователя сигналов управления мультиплексором. Формирователь сигналов управления выполнен в виде двоичного счетчика с дешифратором.

Функциональная электрическая схема КОИ-3/1 имеет следующее построение (рисунок 4.4.), а временные диаграммы, поясняющие принцип работы КОИ-3/1, приведены на рисунке 4.5.

Рисунок 4.4 - Функциональная электрическая схема КОИ-3/1

Рисунок 4.5 - Временные диаграммы, поясняющие принцип работы КОИ-3/1

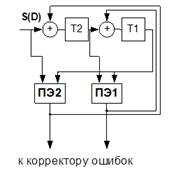

Корректор ошибок декодера выполняется в виде 2 регистров сдвига, каждый из которых содержит по ячеек памяти. На выходе каждого регистра включается сумматор по модулю два, на второй вход которого поступает сигнал коррекции с выхода порогового элемента (ПЭ) анализатора синдромной последовательности (АСП) декодера. Информационные символы с выходов регистров поступают на соответствующие входы КОИ-2/1 декодера.

Важнейшим функциональным блоком декодера ССК с алгоритмом ПД является АСП, который может быть выполнен в виде последовательного регистра, содержащего ячеек памяти, с нумерацией ячеек памяти справа налево, и встроенных сумматоров по модулю два. В состав АСП входят 2 ПЭ, имеющие по входов. Места включения сумматоров по модулю два в регистр и подключение входов ПЭ определяются ненулевыми членами порождающих полиномов.

Пороговое декодирование ССК выполняется с использованием обратной связи в АСП. При этом одновременно с декодированием информационных символов происходит коррекция синдромных символов, использованных при формировании сигнала коррекции. Это выполняется с целью устранения влияния ненулевых символов синдрома на правильное принятие решения при декодировании последующих информационных символов.

Функциональная электрическая схема АСП для рассчитанного ССК имеет следующее построение (рисунок 4.6.).

Рисунок 4.6 - Функциональная электрическая схема АСП

Похожие статьи

-

Разработка и обоснование функциональной электрической схемы кодера БФПС реализован на сумматорах по модулю 2. Информация параллельно приходит на...

-

Рассмотрим кодирование информации на примере систематического ССК с R=1/2 и корректирующего двойные ошибки. Для ССК, как и для блочных циклических кодов,...

-

К основным функциям декодера относятся следующие: 1. Разделение символов входного потока на подпотоков. 2. Формирование последовательности проверочных...

-

Разработка структурной схемы кодера ССК К основным функциям кодера ССК относятся следующие: 1. Разделение символов входного информационного потока на...

-

Систематические СК задаются: 1. с помощью порождающей матрицы, G(D); 2. с помощью проверочной матрицы, Н(D); 3. с помощью разностных треугольников; 4. с...

-

Исходные данные к курсовому проектированию Количество информационных символов k0 = 2 двоичных символа. Количество входов пороговых элементов - 2. Расчет...

-

Определение, параметры и классификация сверточных кодов Сверточные коды (СК) имеют большой научный и практический интерес для современных систем и сетей...

-

Разработка функциональной электрической схемы декодера - Построение декодера Рида - Маллера

При разработке функциональной схемы рассмотрим каждый блок структурной схемы подробнее. Входной регистр. Входной регистр служит для приема всех бит...

-

Пороговое декодирование ССК обеспечивается алгоритмом формирования системы (2) проверочных уравнений (проверок), а именно система проверок формируется...

-

Все основные и вспомогательные параметры, используемые при управлении АСУ ККТХ, сведены в таблице. В таблице указаны верхние и нижние границы их...

-

Выбранные датчики, исполнительные механизмы и их месторасположение, а также структурная схема АСУ ТП производства сухого молока позволяют составить схему...

-

ВВЕДЕНИЕ - Разработка кодека сверточного кода с алгоритмом порогового декодирования

Подавляющее число современных систем связи работает при передаче самого широкого спектра сообщений (от телеграфа до телевидения) в цифровом виде. Из-за...

-

Разработка кодера Хемминга Кодирующее устройство предназначено для кодирования исходной последовательности информационных символов. Для того, чтобы...

-

В процессе анализа элементной базы и существующих устройств был выбран алгоритм работы схемы, подобранна элементная база и разработаны соответствующие...

-

Исходя из результатов, полученных на предыдущем шаге, была построена общая функциональная схема информационно-поисковой системы (рис. 3.12)....

-

Структурная схема АСУ ТП водоснабжения При разработке системы автоматизированного управления технологическим процессом водоснабжения необходимо...

-

Особенности функционального назначения Разрабатываемый программный продукт - это модуль вебсайт для системы управлением контентом портала с архивом...

-

Концепция построения программы Список всех классов приведен на рисунке 3.1. Рисунок 3.1 - Диаграмма классов программы В качестве главного класса...

-

Разработка концептуальной схемы БД Концептуальная схема базы данных формируется путем перехода в Erwin с логического уровня на физический. Все отношения...

-

На выбор типа кода повлиял тот факт, что коды Рида - Маллера являются одним из наиболее старых и хорошо изученных семейств кодов. Хотя минимальное...

-

В данном разделе была разработана функциональная схема работы программного комплекса, которая в общем виде описывает состав комплекса, характер и виды...

-

Для разработки принципиальной электрической схемы, исходя из задания и выбранной элементной базы, составим структурную схему стенда, которая будет иметь...

-

Для иллюстрации последовательности проводимых работ приведем диаграмму Гантта данного проекта, на которой по оси Х изображены календарные дни от начала...

-

СХЕМА АЛГОРИТМА РАБОТЫ ПРОГРАММЫ, ЗАКЛЮЧЕНИЕ - Основы программирования в операционной системе Unix

Блок-схема главной функции программы (main) изображена на рисунке 4. Рисунок 4 - блок-схема main. cpp Блок-схема модуля (Math. cpp) изображена на рисунке...

-

Выбор мобильной платформы и изучение инструментов разработки - Исследование алгоритмов

Практическая реализация алгоритмов, представленных в предыдущих пунктах, предполагает: 1) Выбор мобильной платформы; 2) Изучение соответствующей среды...

-

Функциональная схема включения. - Микропроцессорная техника

Данная функциональная схема используется при работе микропрцессора в максимальном режиме при организациях многопроцессорных систем. При обращенях к...

-

Разработка структурной схемы Для реализации устройства бегущая строка требуется, прежде всего, отображение информации для визуального восприятия, что...

-

Схема реализации функции А Функция А : Функция сброса: Для реализации функции сигнала А нам потребуется: - 2 элемента И, один с двумя входами, один с...

-

Работа программы представлена на рисунке 2.3 Рис. 2.3 Кодирование и тестирование программы Программа кодировалась на языке Си++, используя библотеку Qt5x...

-

Любой компьютер является электроприбором и представляет собой потенциальную угрозу. Поэтому при работе с компьютером следует соблюдать требования...

-

Для того, чтобы строить диаграммы в соответствии с рисунком 2.7, необходимо реализовать алгоритм соединения двух объектов линией. Для отображения линии...

-

Составьте программу для реализации графического редактора линий, изображенного на рисунке 1.1.: Рисунок 1.1. - Пример работы Целью данной работы является...

-

Если в результате поиска на схеме по данным из таблицы будет найдено несколько экземпляров оборудования (т. е. с одинаковой маркировкой или...

-

3.1 Алгоритм функционирования СУ технологического объекта Рисунок 8 - Общий алгоритм функционирования 3.2 Алгоритм запуска технологического объекта...

-

Постановка задачи на разработку программного обеспечения Для того чтобы предлагаемая схема была интегрирована в САПР, который не имеет функции интеграции...

-

Принципиальная электрическая схема определяет полный состав элементов и связей между ними и дает детальное представление о принципах работы объекта...

-

DipTrace имеет интегрированные библиотеки, которые содержат графическую информацию о символах и типовых корпусах компонентов и текстовую упаковочную...

-

В соответствии со структурной схемой разработаем принципиальную схему, выберем компоненты для каждого из введенного блока. В качестве устройства...

-

Разработка алгоритма работы изделия - Разработка интерфейса рекламной бегущей строки

По принципу работы бегущие строки делятся на 2 типа: С динамической разверткой. Могут воспроизводить только текстовую информацию. Текст бегущей строки...

-

Исходя из логики работы схемы, см. пункт 2.1, можно сформулировать следующие критерии отказов: - Отказ любых 2-х элементов из 1,2,3; Отказ 4-го элемента...

РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ КОДЕКА - Разработка кодека сверточного кода с алгоритмом порогового декодирования