Однорозрядні суматори - Суматори. Арифметично-логічні пристрої

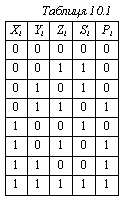

Однорозрядним суматором називається логічна схема, яка виконує додавання значень i-х розрядів Xi та Yi двійкових чисел з урахуванням перенесення Zi з молодшого сусіднього розряду та виробляє на виходах функції результат Si і перенесення Pi в старший сусідній розряд. На основі однорозрядних схем додавання на три входи та два виходи будуються багаторозрядні суматори будь-якого типу. Алгоритм роботи однорозрядного суматора відображається таблицею істинності (табл. 10.1).

На основі табл. 10.1 записується система логічних функцій для результату Si та перенесення Pi у ДДНФ:

(1)

(2)

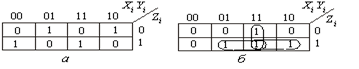

Мінімізація функцій (1) та (2) за допомогою карт Карно показана на рис. 10.1.

Як видно з карт Карно, функція результату Si не мінімізується, а функція Рі мінімізується зі зниженням рангу кон'юнкції та використовує тільки прямі значення змінних:

(3)

Рис. 10.1. Карти Карно для мінімізації функцій: а - Si; б - Рi

При проектуванні комбінаційних однорозрядних суматорів враховують такі чинники:

Схема має характеризуватися регулярністю (подібністю) структури та мінімальною вартістю, тобто мати по можливості найменше число логічних входів всіх елементів;

З метою підвищення швидкодії багаторозрядного суматора потрібен мінімальний час одержання функції перенесення tП=k tР, де k - число послідовно увімкнених елементів від входів до виходів Рi або ; tP - середня затримка розповсюдження сигналу одним логічним елементом в обраній серії інтегральних мікросхем; параметр k часто називають каскадністю (поверховістю) схем. Таким чином, для мінімізації часу одержання перенесення необхідно зменшити каскадність схеми та використати інтегральні мікросхеми з малим часом затримки розповсюдження сигналу;

Для схем однорозрядних суматорів на основі рівнянь (1) і (2) необхідно виробляти як прямі Pi, так й інверсні значення функції перенесення. Така організація перенесень називається парафазною.

Для побудови схеми однорозрядного суматора на універсальних логічних елементах НЕ І рівняння (1) і (2) перетворюються на основі правил подвійної інверсії та де Моргана до такого вигляду:

(4)

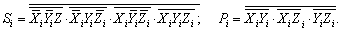

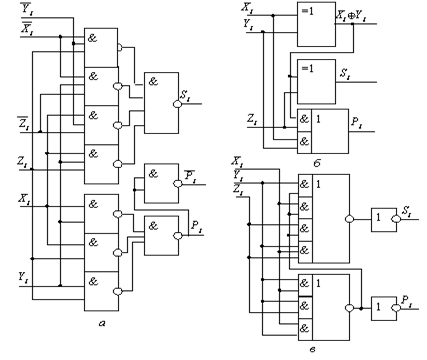

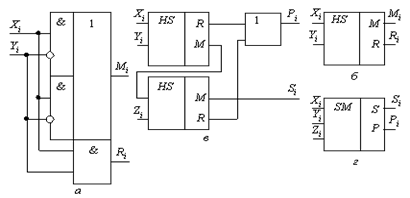

Схема однорозрядного суматора, побудована на елементах НЕ І відповідно до рівнянь (4.30), показана на рис. 10.2, а; її вартість, яка вимірюється числом логічних входів всіх елементів, становить 27, каскадність k=3.

Рівняння (1) та (2) можуть бути виражені через функцію "Виключальне ЧИ":

(5)

(6)

Схема однорозрядного суматора на елементах "виключальне ЧИ" згідно з рівняннями (5) і (6) показана на рис. 10.2, б; її вартість становить вісім входів і каскадність k=2.

Рис. 10.2. Схеми однорозрядних суматорів: а - на елементах НЕ І; б - на елементах "виключальне ЧИ"; в - з використанням власного перенесення

Функції однорозрядного суматора - самоподвійні, тобто їхні інверсії утворюються інвертуванням значень аргументів без зміни місцезнаходження знаків диз'юнкції та кон'юнкції, наприклад, для перенесення з рівняння (2):

(7)

Помножуючи ліві та праві частини співвідношення (7) на макстерм (XiUYiUZi), одержують:

(8)

Після підстановки лівої частини співвідношення (10.8) в праву частину виразу (10.1) одержують рівняння для функції Si з використанням власного перенесення:

(9)

Схема однорозрядного суматора відповідно до рівнянь (9) і (3) показана на рис. 10.2, в; її вартість дорівнює 17 входів, каскадність k=2. Важливою властивістю цієї схеми є використання тільки прямих значень вхідних змінних і однофазного ланцюга формування перенесення Pi в старший розряд.

Напівсуматором називається логічна схема, яка виконує додавання значень i-х розрядів Xi і Yi двійкових чисел X і Y та реалізує на виході значення результату Mi і перенесення в старший сусідній розряд Ri:

(10)

Таким чином, напівсуматор виконує лише частину завдання підсумовування в i-му розряді, оскільки не враховує перенесення з сусіднього молодшого розряду. Схема напівсуматора, побудована на основі рівнянь (10.10), показана на рис. 10.3. З рівнянь (10.5) і (10.6) виходить, що схема однорозрядного суматора може бути побудована на основі двох напівсуматорів і додаткового логічного елемента ЧИ, як показано на рис. 10.3, в.

Рис. 10.3. Схеми підсумовування: а, б - напівсуматор і його умовне

Позначення; в, г - однорозрядний суматор і його умовне позначення

Похожие статьи

-

Двійково-десяткові суматори - Суматори. Арифметично-логічні пристрої

Двійково-десяткові суматори використовуються для обробки масивів десяткової інформації за порівняно простими алгоритмами, оскільки при цьому вилучаються...

-

Загальна характеристика суматорів - Суматори. Арифметично-логічні пристрої

Суматором називається функціональний вузол комп'ютера, призначений для додавання двох n-розрядних слів (чисел). Операція віднімання заміняється...

-

Послідовний двійковий багаторозрядний суматор містить: N-розрядні зсуваючі регістри операндів X і Y, регістр результату S, однорозрядний суматор SM і...

-

Мікросхеми ALU - Суматори. Арифметично-логічні пристрої

Суматор арифметичний мікросхема логічний Промисловість випускає мікросхеми із символом функції ALU для виконання 16 арифметичних та 16 порозрядних...

-

Перші програмовані інтегральні мікросхеми можна віднести до програмованих логічних пристроїв (ПЛП). Вони з'явилися в 70-ті роки у вигляді мікросхем ППЗП...

-

Опорно-поворотні пристрої, Висновок - Супутникові системи зв'язку

Для точної орієнтації параболічної антени на ІСЗ в її конструкції необхідно передбачити поворотні механізми, які дозволяють змінювати положення антени по...

-

За умовою вихідних даних курсової роботи зобразимо структурну схему ЦАП на основі матриці типу R-2R. Рисунок 3.1- Cхема ЦАП на основі матриці R-2R...

-

Схеми ПЛМ досить громіздкі, і тому зображати їх бажано з максимально можливим спрощенням. Використовуються зображення, в яких багатовходові елементи І,...

-

За вихідними даними нам потрібно реалізувати: формувач сигналу, що реалізує функцію 4-х вхідних сигналів за ознакою більшості; формувач сигналів Fx та...

-

СХЕМА СРАВНЕНИЯ КОДОВ - Цифровые устройства и микропроцессоры

Два кода X и Y считаются равными, если попарно равны их одноименные разряды. Можно ввести функцию F(X==Y), которая равна 1, если xi=yi для всех i, иначе...

-

СУММАТОРЫ - Цифровые устройства и микропроцессоры

Сумматор осуществляет арифметическое суммирование n-разрядных кодов X=(x(n-1),..,x0) и Y=(y(n- 1),..,y0). Правила сложения двух одноразрядных двоичных...

-

ВИСНОВКИ - Розрахунки та проектування аналогово-цифрових та цифро-аналогових перетворювачів

Під час виконання курсової роботи було проведено ряд розрахункових параметрів які необхідні для проектування схем АЦП і ЦАП. Була визначена частота...

-

Вариант № 6 Необходимо разработать цифровое комбинационное устройство демультиплексор из 1 в 4 в базисе ИЛИ-НЕ, НЕ, логическая функция которого указана...

-

Задача Рассмотрим поведение коэффициента равноправия разделения ПС для протоколов TCP и ARTCP в зависимости от числа соединений. Поведение коэффициента F...

-

Розроблений пристрій призначений для проведення лабораторної роботи з предмету "Цифрова схемотехніка". Він дозволяє дослідити та наочно показати роботу...

-

Цифровые устройства и микропроцессоры

Введение Счетчики выполняют на запоминающих элементах - триггерах. Он фиксирует число импульсов, поступивших на его вход. В интервалах между ними счетчик...

-

Аналітичні методи побудови перехідних характеристик грунтуються на розв'язку диференціального рівняння системи. Для цього може бути використаний як...

-

Заключение - Конструирование СВТ

В данном курсовом проекте было разработано арифметическое устройство для выполнения сложения и вычитания десятичных чисел. На вход схемы подаются два...

-

Схемы применения цифро-аналоговых преобразователей относятся не только к области преобразования код - аналог. Пользуясь их свойствами можно определять...

-

Мета роботи: дослідження впливу зміни технічного стану окремих вузлів на поведінку діагностичних параметрів ГТД та набуття досвіду роботи з ЕОМ у...

-

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПАМЯТЬ) - Цифровые устройства и микропроцессоры

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и...

-

ПРИМЕНЕНИЕ СЧЕТЧИКОВ В ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ - Цифровые устройства и микропроцессоры

На рисунке внизу последовательно включены 6 счетчиков с модулем 10 (двоично - десятичные). Информационные выходы Qi каждого каскада через преобразователь...

-

РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА - Цифровые устройства и микропроцессоры

Название указывает, что сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую. Одна из возможных схем трехразрядного...

-

Введение - Преобразователи кода

Цифровые устройства в настоящее время широко используются во всех отраслях: связь, телевидение, управление промышленным и бытовым оборудованием,...

-

Радиорелейный диапазон тракт абонент На рис. 3 показана структурная схема оконечной станции ЦРРЛ. На оконечной станции линейный цифровой сигнал ЛЦС в...

-

В основе развития этого класса методов лежит утверждение, что анализ речи, основанный на модели слуха человека, будет более успешным, чем анализ,...

-

Определение годового объема работ в СЦ - Проект реконструкции сервисного центра ООО "Авторесурс"

Часть владельцев автомобилей выполняют ТО и ТР собственными силами или с привлечением других лиц и т. д., т. е. не все автомобили, которым необходимо ТО...

-

Схема трансивера с указанием основных соединений представлена на рисунке 5.1. Рисунок 5.1 Рассмотрим более подробно каждый блок в отдельности: Фильтр...

-

Так як ми вже визначились зі структурною схемою приладу, то потрібно розробити електричну принципову. Спочатку визначимось з усіма складовими окремо. В...

-

На исследуемом перекрестке имеется четыре регулируемых пешеходных перехода с каждого входа. Масштабный план перекрестка ул. Кирова - проспект Победы...

-

Была изучена работа перекрестка проспект Победы - улица Кирова г. Гомеля, а также приведена дислокация ТСОДД на данном перекрестке. Приведены результаты...

-

Швидке перетворення Фур'є - Розробка процесора ШПФ

Вихідними даними для ШПФ є елементи обмеженої послідовності x(n), де n=0,1,.. N-1. Відповідно дискретне перетворення Фур'є має вид: (1) (2) Де -...

-

АЦП и ЦАП - Современные звуковые карты. Методы позиционирования и сжатия звука

Аналогово-цифровой и цифро-аналоговый преобразователи. Первый преобразует аналоговый сигнал в цифровое значение амплитуды, второй выполняет обратное...

-

Уменьшение потерь в стабилизаторах - Интегральный линейный стабилизатор напряжения

Требуемое для нормальной работы интегрального стабилизатора на рис. 2 минимальное падение напряжения на нем составляет около 3 вольт. Для схем,...

-

Аттенюаторы и интеграторы на ЦАП - Цифро-аналоговый преобразователь с параллельным интерфейсом

Аттенюаторы, т. е. регуляторы уровня сигнала, с цифровым управлением гораздо более надежны и долговечны, чем традиционные аттенюаторы на основе...

-

Общая схема модельного эксперимента Проведенный в рамках диссертации модельный эксперимент ставил задачей определение эффективности работы сети с...

-

Рисунок 3.1 - Структурна схема системи автоматичного регулювання температури в печі Для знаходження передаточних функцій системи за каналами задаючої і...

-

Основные научные результаты диссертации состоят в следующем: Разработан протокол ARTCP, использующий темпоральные показатели потока в качестве входного...

-

Последовательный ЦАП на переключаемых конденсаторах - цифро-аналоговые преобразователи

Рассмотренная выше схема ЦАП с ШИМ вначале преобразует цифровой код во временной интервал, который формируется с помощью двоичного счетчика квант за...

-

Аналоговые мультиплексоры - Аналоговые коммутаторы

Хорошим приложением ключей на полевых транзисторах являются мультиплексоры - схемы, которые позволяют выбрать один из нескольких входов по указанию...

Однорозрядні суматори - Суматори. Арифметично-логічні пристрої