Разработка принципиальных схем функциональных блоков - Разработка кодека сверточного кода с алгоритмом порогового декодирования

При разработке принципиальных электрических схем функциональных блоков кодека необходимо выполнение следующих требований [2]:

- 1. Простота схемотехнических решений. 2. Патентная чистота схемотехнических решений или оригинальность данных решений. 3. Наличие встроенных автоматизированных систем технического контроля и диагностики кодека. 4. Минимальный объем оборудования кодека.

Принципиальные электрические схемы кодера и декодера представлены в приложении 1 и приложении 2 соответственно.

КРИ-1/2 КРИ-1/3

Эти блоки могут быть реализованы с помощью следующих интегральных микросхем (ИМС): КР1533ИЕ5, КР1533ЛИ3, КР1533ТМ8.

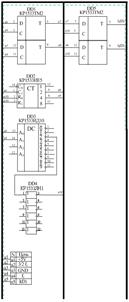

Микросхема КР1533ИЕ5 представляет собой четырехразрядный двоично-десятичный счетчик, микросхема КР1533ЛИ3 - три идентичных трехвходовых логических элемента 3И со стандартными выходами ТТЛ. Конструктивно связанные микросхемы КР1533ЛИ3 и КР1533ИЕ5 используются для реализации делителя частоты на семь и на восемь для КРИ-1/7 КРИ-1/8 соответственно. Распределение входящей последовательности осуществляется с использованием 4 микросхем КР1533ТМ8, каждая из которых представляет собой четыре синхронных D-триггеров с прямыми и инверсными выходами. Принципиальная схема КРИ 1/2 представлена на рисунке 5.1.

Рисунок 5.1 - Принципиальная схема КРИ 1/2

ФПСк и ФПСд

Данные блоки реализованы на следующих ИМС: КР1533ТМ8 и КР1533ЛП5.

Микросхема КР1533ЛП5 содержит четыре независимых элемента "исключающее ИЛИ" со стандартными выходами ТТЛ. Принципиальная схема ФПСк приведена на рисунке 5.2.

КОИ 3/1 и КОИ 2/1

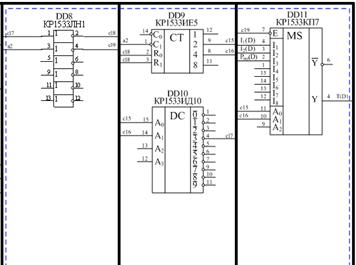

Эти блоки реализованы на ИМС КР1533КП7, КР1533ЛН1, КР1533ИЕ5.

Микросхема КР1533КП7 представляет собой селектор-мультиплексор 8 к 1 и в зависимости от кода, установленного на адресных входах А1 - А3, разрешает прохождение сигнала на выходы Y и только одного из восьми информационных входов D0 - D7, при этом на входе стробирования должно быть установлено напряжение низкого уровня U0, КР1533ЛН1 - шесть элементов НЕ. Принципиальная схема КОИ 3/1 приведена на рисунке 5.3.

Рисунок 5.3 - Принципиальная схема КОИ 3/1

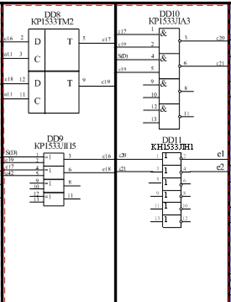

АСП и ФСП

Блок АСП реализуется с использованием ИМС КР1533ТМ8 и КР1533ЛП5. Принципиальная электрическая схема ПЭ декодера ССК может быть выполнена с применением ИМС КР1533ЛИ1.

Блок ФСП реализован на одной микросхеме КР1533ЛП5.

Принципиальная схема АСП с двумя ПЭ представлена на рисунке 5.4.

Рисунок 5.4 - Принципиальная схема АСП

Корректор ошибок

Корректор ошибок (КО) декодера выполняется в виде семи регистров сдвига, каждый из которых содержит 7 ячеек памяти. Коррекция информационных символов может осуществляться с применением микросхем КР1533ТМ9 и одного сумматора по модулю два микросхемы КР1533ЛП5. Принципиальная схема КО представлена на рисунке 5.5.

Похожие статьи

-

Разработка структурной схемы кодера ССК К основным функциям кодера ССК относятся следующие: 1. Разделение символов входного информационного потока на...

-

Критерием выбора принципа построения функциональных блоков кодека является обеспечение минимума сложности аппаратной реализации. В соответствии с [1-3]...

-

К основным функциям декодера относятся следующие: 1. Разделение символов входного потока на подпотоков. 2. Формирование последовательности проверочных...

-

Систематические СК задаются: 1. с помощью порождающей матрицы, G(D); 2. с помощью проверочной матрицы, Н(D); 3. с помощью разностных треугольников; 4. с...

-

Выбор и обоснование элементной базы Выбор элементной базы производится по следующим правилам [6]: Верхняя граничная частота ИМС должна быть в 2 - 3 раза...

-

ВВЕДЕНИЕ - Разработка кодека сверточного кода с алгоритмом порогового декодирования

Подавляющее число современных систем связи работает при передаче самого широкого спектра сообщений (от телеграфа до телевидения) в цифровом виде. Из-за...

-

Пороговое декодирование ССК обеспечивается алгоритмом формирования системы (2) проверочных уравнений (проверок), а именно система проверок формируется...

-

Рассмотрим кодирование информации на примере систематического ССК с R=1/2 и корректирующего двойные ошибки. Для ССК, как и для блочных циклических кодов,...

-

Исходные данные к курсовому проектированию Количество информационных символов k0 = 2 двоичных символа. Количество входов пороговых элементов - 2. Расчет...

-

Определение, параметры и классификация сверточных кодов Сверточные коды (СК) имеют большой научный и практический интерес для современных систем и сетей...

-

В процессе анализа элементной базы и существующих устройств был выбран алгоритм работы схемы, подобранна элементная база и разработаны соответствующие...

-

Разработка функциональной электрической схемы декодера - Построение декодера Рида - Маллера

При разработке функциональной схемы рассмотрим каждый блок структурной схемы подробнее. Входной регистр. Входной регистр служит для приема всех бит...

-

Блок TIMER обеспечивает возможность синхронизации событий процесса или создание заданных задержек. На рисунке он имеет следующий вид. Рис. 37.1...

-

Выбранные датчики, исполнительные механизмы и их месторасположение, а также структурная схема АСУ ТП производства сухого молока позволяют составить схему...

-

Блок накопителя импульсного входа (Pulse Input Totalizer Block) предоставляет функция накопления расхода, дополняющую блок канала импульсного входа...

-

Описание Блок PIDFF подобный блока PID, но он еще дополнительный вход сигнала опережение. Пользователь может настроить блок PIDFF таким образом, что...

-

Блок FLAGARRAY, Вход/Выход, Блок TEXTARRAY - Библиотека функциональных модулей системы EXP PKS

Функциональный блок FLAGARRAY обеспечивает хранение 1000 значений с двумя состояниями. Доступ к значению можно осуществить как к простому булеву значению...

-

Структурная схема АСУ ТП водоснабжения При разработке системы автоматизированного управления технологическим процессом водоснабжения необходимо...

-

Блок - схема алгоритму, Опис алгоритму - Розробка гри в С# "Корови та бики"

Рисунок 2.1 - Блок - схема алгоритму роботи програми Рисунок 2.1 (продовження) Опис алгоритму 3.1. Робота програми розпочинається з виділення пам'яті під...

-

Описание Блок TYPECONVERT входит в СЕЕ предоставляет возможность преобразования данных одного типа в другой для соединения параметров разных типов. Он...

-

Как в существующем Experion PKS блоки модуля ввода - вывода, данные контроля (управления) не сделаны доступными через блок модуля. Вместо этого, блоки...

-

Описание Блок AICHANNEL является блоком аналогового входа, он позволяет записать до восьми выражений для вычисления. Каждое выражение может выполнять...

-

Поскольку вывод передаточной функции трехфазного двигателя достаточно громоздкий, предположим, что в погружных насосах скважин используются двигатели...

-

Для разработки принципиальной электрической схемы, исходя из задания и выбранной элементной базы, составим структурную схему стенда, которая будет иметь...

-

Интересной особенностью блока питания принтера Epson DFX-8000 является наличие схемы, контролирующей уровень первичного напряжения. Схема состоит из...

-

Все основные и вспомогательные параметры, используемые при управлении АСУ ККТХ, сведены в таблице. В таблице указаны верхние и нижние границы их...

-

Разработка концептуальной схемы БД Концептуальная схема базы данных формируется путем перехода в Erwin с логического уровня на физический. Все отношения...

-

Описание Блоки функций обмена предоставляют различные конфигурируемые функции для записи и считывания данных управления. Есть три разновидности этих...

-

Блок REQTEXTARRAY обеспечивает хранение 64 символов ASCII, которые доступны с помощью соответствующих строковых параметров конфигурации (STR[n]).Здесь...

-

Блок SWITCH принимает до восьми инициализируемых входов и работает как однополюсный восьмипозиционный поворотный переключатель. Положение переключателя...

-

Блок PULSELENGTH генерирует последовательности импульсов в соответствии с алгоритмом управления с широтно-импульсной модуляцией. Импульсный выход обычно...

-

Блок OVRDSEL принимает до четырех входов (от первичных блоков) и выбирает один с наибольшим или наименьшим значением. Графически это выглядит следующим...

-

Особенности функционального назначения Разрабатываемый программный продукт - это модуль вебсайт для системы управлением контентом портала с архивом...

-

В соответствии со структурной схемой разработаем принципиальную схему, выберем компоненты для каждого из введенного блока. В качестве устройства...

-

Исходя из разработанной структурной схемы, можно выделить следующие части проектируемой схемы. Аналого-цифровой преобразователь должен преобразовывать...

-

Блок LEADLAG, Вход, Выход, Блок POSPROP - Библиотека функциональных модулей системы EXP PKS

Блок LEADLAG обеспечивает динамическую компенсацию опережения-задержки изменения значения входа (P1). Он преобразует изменение значения входа (P1) с...

-

Позволяет настроить до десяти отдельных входов для расчета значения переменной (PV), которые можно масштабировать и смещать. Блок AUXSUMMER извлекает...

-

Разработка и обоснование функциональной электрической схемы кодера БФПС реализован на сумматорах по модулю 2. Информация параллельно приходит на...

-

Исходя из логики работы схемы, см. пункт 2.1, можно сформулировать следующие критерии отказов: - Отказ любых 2-х элементов из 1,2,3; Отказ 4-го элемента...

-

Назначение компонентов и работа схемы - Разработка интерфейса рекламной бегущей строки

В заключении раздела рассмотрим связь элементов, каскадов с соответствующими параметрами изделия. Каскады усилителей низкой частоты можно соединять при...

Разработка принципиальных схем функциональных блоков - Разработка кодека сверточного кода с алгоритмом порогового декодирования