Схема ДТЛ - диодно-транзисторной логики - Электроника и схемотехника аналоговых устройств

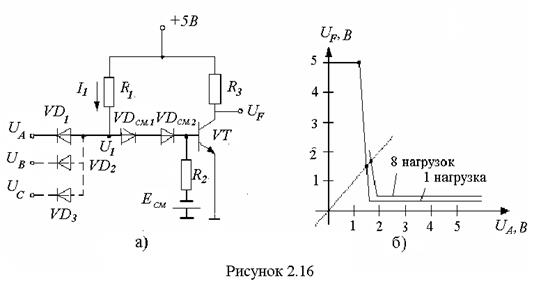

Основная схема ДТЛ приведена на рисунке 2.16,а. Здесь диоды VD1, VD2, VD3 и резистор R1 представляют собой конъюнктор (И), элементы VT, R2, R3 _ инвертор (НЕ), смещающие диоды VDСМ1, VDСМ2 - осуществляют связь между логическими элементами И и НЕ и смещают (понижают) потенциал базы VT относительно напряжения U1. Резистор R2 служит для подачи смещения ЕСМ на VT и гарантированного удерживания его в запертом состоянии при открытых входных диодах и как дополнительная цепь обратного тока базы при запирании транзистора.

При высоком уровне напряжения на входе UA = UB = UC = U1, диоды VD1...VD3 заперты, повышается потенциал точки U1, отпираются диоды смещения VDСМ1, VDСМ2, течет ток базы VT, и транзистор входит в насыщение. Напряжение на коллекторе UF падает до нуля, т. е. F = 0.

Если хотя бы на одном из входов низкий уровень напряжения UA или UB или UC равен U0, отпирается соответствующий диод, понижается потенциал U1, запираются диоды смещения VDCМ1, VDСМ2. На базе транзистора VT низкое напряжение, который запирается. UВЫХ = UF = U1, т. е. на выходе элемента появляется логическая единица.

Если отбросить часть схемы (см. рисунок 2.16,а), изображенную пунктиром, она превращается в инвертор. На рисунке 2.16,б приведена ее передаточная характеристика UF = f(UA),

Если напряжение на входе А равно 0, то диод VD1 смещен в прямом направлении и напряжение U1 равно +0,6 В. Эта величина недостаточна для открывания диодов VDСМ1, VDСМ2 и перехода база-эмиттер транзистора VТ. Поэтому ток I1 течет через диод VD1, источник сигнала UA и на землю. Транзистор VТ закрыт, при этом UF = +5 В. Если UA увеличивается, то U1 также растет до тех пор, пока не достигнет 1,2 В. В этот момент VDСМ1, VDСМ2, VТ открываются и ток I1 течет через транзистор VТ и переводит его в насыщение. Дальнейшее увеличение напряжение UA запирает диод VD1. но не может повлиять на величину U1 или состояние транзистора VТ. Из графика видно, что интервалы напряжений, соответствующие логическим состояниям 0 и 1, примерно равны 0 ? U0 ? 1,2 B, 1,5 ? U1 ? 5 В.

Практически U0 обычно меньше 0,4 В, а U1 очень близко к 5 В, что обеспечивает хороший шумовой запас по постоянному току.

Если на вход подано напряжение, соответствующее логической 1, то диод VD1 смещен в обратном направлении и, следовательно, потребляет минимальную мощность с выхода предыдущей схемы. Однако, если на входе поддерживается напряжение логического 0, то ток I1 должен течь из входной клеммы элемента через насыщенный транзистор на землю. Это соответствует одной единичной нагрузке. Если к одному выходу подсоединено n входов, то насыщенный транзистор должен пропускать ток, в n раз больше чем I1. Если n увеличивается, то будет расти и напряжение UА, что эквивалентно увеличению напряжения выходного транзистора. Этот эффект приведен на рисунке 2.16,б, где передаточная характеристика изображена для случая одной выходной единичной нагрузки и для случая восьми единичных нагрузок (максимально допустимое количество для базового элемента ДТЛ).

Если к схеме, в соответствии с рисунком 2.16,а, добавить диоды VD2, VD3, то напряжение UF будет соответствовать логической 1, если хотя бы один из входов будет в состоянии логического нуля. Логический нуль на выходе можно получить только в том случае, если на всех входах присутствует напряжение логической единицы, т. е. логическая операция, выполняемая данной схемой, имеет вид:

,

Что соответствует операции И-НЕ. Добавлением дополнительных диодов для расширения объема входа число входов в базовом элементе ДТЛ И-НЕ может быть доведено до 20.

Задержка передачи для типичного элемента ДТЛ составляет 30 нс. Это сравнительно большая величина во многих случаях оказывается вполне приемлемой.

Похожие статьи

-

Схемы ЭСЛ _ эмиттерно-связанной логики - Электроника и схемотехника аналоговых устройств

Цифровые микросхемы эмиттерно-связанной логики имеют более высокое быстродействие, чем схемы ТТЛ (даже ценой большей рассеиваемой мощности), достигшее в...

-

Схемы ТТЛ _ транзисторно-транзисторной логики - Электроника и схемотехника аналоговых устройств

Разновидности схем ТТЛ Также широко используются на практике разновидности схем ТТЛ: А) схема ТТЛ с тремя состояниями выхода Схемы базовых ТТЛ нельзя...

-

Входная и выходная характеристики транзистора с ОЭ несколько отличаются от характеристик транзистора с ОБ. Входной характеристикой транзистора,...

-

Ключевой режим работы транзистора - Электроника и схемотехника аналоговых устройств

1. Транзисторный ключ с общим эмиттером Наибольшее распространение в цифровой и импульсной технике имеет ключ с общим эмиттером. В схеме - коллекторная...

-

Основные параметры логических интегральных микросхем Входное U1вх и выходное U1вых напряжения логической единицы - значение высокого уровня напряжения на...

-

Полупроводниковые твердые схемы - Электроника и схемотехника аналоговых устройств

Твердые схемы представляют собой устройства, состоящие из кристаллов полупроводника, выполняющих функции активных и пассивных элементов схемы без внешних...

-

1. Физическая Т-образная эквивалентная схема На рисунке 5.12 приведена физическая Т-образная эквивалентная схема транзистора с общей базой, где:?...

-

Для целенаправленного изменения свойств полупроводники легируют, т. е. вводят в небольшом количестве атомы примесей, позволяющие управлять типом...

-

Оптоэлектронные полупроводниковые приборы - Электроника и схемотехника аналоговых устройств

Оптоэлектроника - область электроники, занимающаяся вопросами преобразования оптических сигналов в электрические и наоборот. Новое направление в...

-

Перспективы развития электроники - Электроника и схемотехника аналоговых устройств

Современные состояние развития электроники заключается в переход от микротехнологии к нанотехнологии. Прогресс в развитии науки и технологии,...

-

Переключательные полупроводниковые приборы - Электроника и схемотехника аналоговых устройств

К переключательным полупроводниковым приборам относятся тиристоры, однопереходные и лавинные транзисторы. Тиристоры - это многослойные переключающие...

-

Полевые транзисторы - Электроника и схемотехника аналоговых устройств

Полевой транзистор - это полупроводниковый прибор, работа которого основана на модуляции сопротивления полупроводника поперечным электрическим полем...

-

Для реальных структур Сопротивление эмиттерного перехода мало (сотни омов), а сопротивление коллекторного перехода составляет сотни килоом. Допустим, в...

-

Полупроводниковый резистор - это полупроводниковый прибор с двумя выводами, построенный на полупроводнике, равномерно легированном примесями. В...

-

"Введение, этапы развития электроники" - Электроника и схемотехника аналоговых устройств

Электроника-область науки, техники и производства, охватывающая изучение физических основ, исследование, разработку и принципы использования приборов,...

-

Помимо аналого-цифровых преобразователей (АЦП), работой цифровой логики могут управлять операционные усилители (ОУ) и компараторы, преобразующие...

-

Нанесение защитной пленки диэлектрика (Si02) - Электроника и схемотехника аналоговых устройств

После формирования кремниевой подложки наступает этап создания сложнейшей полупроводниковой структуры. Для этого в кремний нужно внедрить так называемые...

-

Микроэлектроника - Электроника и схемотехника аналоговых устройств

Интеграмльная (микро)схемма (ИС, ИМС, м/сх, англ. integrated circuit, IC, microcircuit), чип, микрочимп (англ. microchip, silicon chip, chip -- тонкая...

-

"Физические явления при контакте твердых тел" - Электроника и схемотехника аналоговых устройств

При образовании кристаллической решетки металла внешние валентные электроны оказываются настолько слабо связанными со своими ядрами, что под воздействием...

-

ТРИСТАБИЛЬНЫЕ ЭЛЕМЕНТЫ - Цифровые устройства и микропроцессоры

Наряду с двумя логическими состояниями существует третье технологическое состояние, когда выход элемента отключается от внутренней схемы. При этом...

-

Биполярные транзисторы - Электроника и схемотехника аналоговых устройств

Транзисторами называются полупроводниковые приборы, способные усиливать электрическую мощность, имеющие три или более выводов, один или более p-n...

-

Для n-логических переменных (аргументов) существует 2n их комбинаций или двоичных наборов. На каждом таком наборе может быть определено значение функции...

-

КОМБИНАЦИОННЫЕ СХЕМЫ, ДЕШИФРАТОР - Цифровые устройства и микропроцессоры

В комбинационных схемах логическая функция зависит только от комбинации значений входных переменных. При описании многих цифровых устройств невозможно...

-

Расчет схемы электрической принципиальной цифрового матрицирующего устройства. Рассмотрим систему обозначений сигналов, принятую в цифровом телевидении...

-

Построение структурной схемы автомата (рис. 10) осуществляется по результатам минимизаций функций по картам Карно. Схема состоит из четырех блоков:...

-

Вариант № 6 Необходимо разработать цифровое комбинационное устройство демультиплексор из 1 в 4 в базисе ИЛИ-НЕ, НЕ, логическая функция которого указана...

-

Разработка функциональной схемы устройства - Разработка автомобильной охранной сигнализации

Функциональная схема автомобильной сигнализации показана на рисунке 6. Функциональная схема брелока управляющего автомобильной сигнализацией показана на...

-

Генератор тактовых импульсов должен вырабатывать прямоугольные импульсы частотой 190 Гц. В качестве токового возьмем мультивибратор на логических...

-

Принципиальная схема устройства - Радиосистема пожарной сигнализации

Исходя из технических требований и структурной схемы, выберем схемы и элементную базу для устройства. В качестве генератора колебаний используем простой...

-

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти...

-

Синтез счетной схемы - Синтез дискретного устройства

Как видно из таблицы 1.1 и выражений для функций, реализуемых дешифраторами, для правильной работы дискретного устройства достаточно получить младшие 4...

-

ЛОГИЧЕСКИЙ БАЗИС, СХЕМНЫЕ ОСОБЕННОСТИ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ - Цифровые устройства и микропроцессоры

Набор простейших ЛФ, позволяющих реализовать любую другую функцию называется логическим базисом (ЛБ). Функции И, ИЛИ, НЕ не являются минимальным ЛБ, т....

-

Основные сведения об элементной базе устройства - Плата КП632

Устройство построено на цифровых элементах. Элемент DD1 представляет собой микросхему 133АГ3. Рис. 1.1. Микросхема К155АГ3 Микросхема К155АГ3 (рис. 1.1)...

-

Элементы промышленной электроники - Общая электротехника и электроника

Выпрямители . Выпрямитель - это устройство, предназначенное для преобразования переменною напряжения в постоянное. В зависимости oт числа фаз питающего...

-

D - ТРИГГЕР СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ - Цифровые устройства и микропроцессоры

D - триггер имеет два входа: информационный вход D(аtа) и вход управления записью/запоминанием (защелкиванием) L(oad)/L(atch) - отсюда его второе имя :...

-

Амплитудный детектор на диоде Классическая схема "последовательного" детектора дана на рисунке (собственно, это однополупериодный выпрямитель). Если...

-

Электрическая функциональная схема арифметического устройства для выполнения сложения и вычитания десятичных чисел представлена на рис. 2.4. Отдельно...

-

Выбор и обоснование принципиальной схемы предварительного усилителя ФПУ В соответствии со структурной схемой приведенной ранее, ФПУ конструктивно делится...

-

Рассчитываем элементы схемы автогенератора, Расчет ГУНа - Разработка радиопередающего устройства

Для улучшения стабильности частоты целесообразно выбрать контур с высокой добротностью (Qнен - добротность ненагруженного контура ) и большим...

-

В данной работе разрабатывается микропроцессорная система минимальной конфигурацией, что предполагает использование управляющих сигналов, формируемых...

Схема ДТЛ - диодно-транзисторной логики - Электроника и схемотехника аналоговых устройств