Синтез делителя частоты - Синтез дискретного устройства

На вход делителя частоты поступают сигналы от генератора тактовых импульсов с частотой 190 Гц. На выходе схема должна выдать импульсы с частотой 0,1 Гц. Исходную частоту надо поделить на 1900. Это можно сделать при помощи последовательного соединения делителей на 19, 5, 5, 4.

Делитель на 19.

Реализуем на 5 последовательно включенных JK-триггерах.

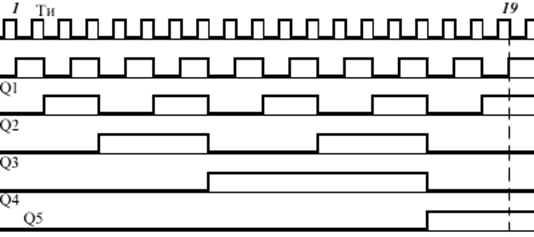

Временная диаграмма представлена на рис. 1.6.

Рис. 1.6. Временная диаграмма работы делителя на 19.

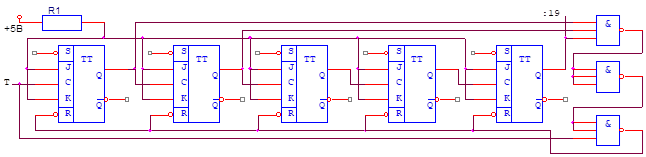

Как видно из рис. 1.6 после прихода 19 импульса на выходах триггеров сформировалась комбинация 10011. При этом комбинация Q5Q2Q1 впервые появляется после 19 импульса. Эту комбинацию используем для определения момента сброса триггеров в ноль, тем самым получая на выходе Q5 схемы 1 импульс (при этом на вход Q1 поступило 19 импульсов). Полная схема делителя на 19 приведена на рис. 1.7.

Рис.1.7. Делитель частоты на 19.

Делитель на 5

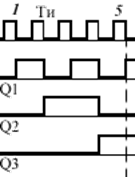

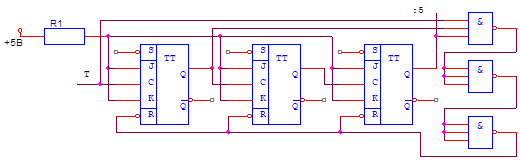

Делитель составим из 3 последовательно включенных JK-триггеров. Временные диаграммы работы делителя приведены на рис. 1.8.

При построении делителя воспользуемся тем же принципом, что и при синтезе делителя на 19.

После прихода 5 импульса на выходах появиться код 101. Комбинация Q3Q1 впервые появляется с приходом 5 импульса. При появлении 6 импульса все триггеры должны сброситься, а поскольку используются двухступенчатые триггеры, то по окончанию 6 импульса делитель посчитает его как 1. Поскольку сброс триггеров будет зависеть от переходных процессов в микросхемах ТТЛ, то во избежание ошибок при установке в 0 после 5 импульса необходимо замедлить переходные процессы. С этой целью в схему ставим еще два инвертора. Полная схема делителя на 5 приведена на рис. 1.9.

Рис. 1.8. Временная диаграмма работы делителя на 5.

Рис. 1.9. Схема делителя частоты на 5.

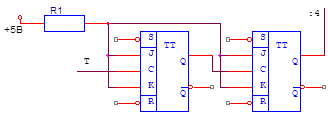

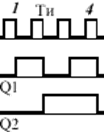

Делитель на 4

Рис. 1.10. Временные диаграммы работы делителя на 4.

Делитель на 4 получается при последовательном соединении двух JK-триггеров. Временная диаграмма работы такого делителя приведена на рис. 1.10, а полная схема на рис. 1.11.

Рис. 1.11 Схема делителя на 4.

Похожие статьи

-

Параметры синтезируемого автомата. Значения сигналов:a, ay.............00 b, by.............01 c, cy.............11 d, dy.............10 Используемые...

-

Генератор тактовых импульсов должен вырабатывать прямоугольные импульсы частотой 190 Гц. В качестве токового возьмем мультивибратор на логических...

-

Синтез счетной схемы - Синтез дискретного устройства

Как видно из таблицы 1.1 и выражений для функций, реализуемых дешифраторами, для правильной работы дискретного устройства достаточно получить младшие 4...

-

Частота генератора тактовых импульсов, Гц....190 Счет ведется от числа....9 Шаг...............................1 Число состояний системы............8...

-

Введение, Синтез дискретного устройства - Синтез дискретного устройства

Целью настоящего курсового проекта является синтез логических схем дискретных устройства и конечного автомата и разработка для них печатных плат. Синтез...

-

АСИНХРОННЫЙ СЧЕТЧИК C ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В качестве примера возьмем четырехразрядный счетчик. Четыре двоичных разряда счетчика обеспечивают М = 16 состояний. Ниже приведена схема и условное...

-

На выходе устройства в качестве буферного каскада применяется последовательная RC -цепь, состоящая из резистора =1 кОм и конденсатора =0,1 мкФ...

-

Заключение, Список использованной литературы - Синтез дискретного устройства

В дискретном устройстве задействовано 15 корпусов микросхем. Устройство выполнено на двух печатных платах. На одной плате располагаются генератор...

-

Пока в энергосистеме имеется вращающийся резерв активной мощности, системы регулирования частоты и мощности будут поддерживать заданный уровень частоты....

-

Частотозадающий конденсатор определяет частоту собственных колебаний ГУН. Его номинал определим в соответствии с зависимостью частоты свободных колебаний...

-

Схемы устройств согласования и защиты - Рельсовые цепи тональной частоты

Схема устройства согласования и защиты зависит от решаемых задач (см. п. 2.4.1) и условий применения. Условия применения определяются наличием или...

-

Классификация систем синхронизации Синхронизация есть процесс установления и поддержания определенных временных соотношений между двумя и более...

-

Расчет схемы электрической принципиальной цифрового матрицирующего устройства. Рассмотрим систему обозначений сигналов, принятую в цифровом телевидении...

-

Термином оптимальный синтез определяют процесс построения устройства с заданными свойствами, оптимально учитывающий совокупность технико-экономических...

-

Mobile. Синтез русской речи для мобильных устройств на базе MS Windows Mobile - Кодировщики голоса

Назначение и области применения: VitalVoice Mobile предназначен для автоматического преобразования произвольного текстового файла в речь на мобильном...

-

Перемножители и делители функций - Цифро-аналоговый преобразователь с параллельным интерфейсом

Как уже указывалось выше, ЦА-преобразователи на МОП-ключах, допускают изменение опорного напряжения в широких пределах, в том числе и смену полярности....

-

Специальный вид автоматики АПВ после АЧР - Коммутационные устройства

Для ускорения восстановления питания потребителей, отключенных при срабатывании АЧР, применяется специальный вид автоматики--АПВ после АЧР (или ЧАПВ)....

-

Измерение частоты - Оcновы радиоэлектроники

Измерение частоты является одной из важнейших задач, решаемых в радиоэлектронике, так как, с одной стороны, частота является одной из основных...

-

ПРИМЕНЕНИЕ СЧЕТЧИКОВ В ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ - Цифровые устройства и микропроцессоры

На рисунке внизу последовательно включены 6 счетчиков с модулем 10 (двоично - десятичные). Информационные выходы Qi каждого каскада через преобразователь...

-

КАСКАДНОЕ ВКЛЮЧЕНИЕ СЧЕТЧИКОВ, СЧЕТЧИК - ТАЙМЕР - Цифровые устройства и микропроцессоры

Рассмотрим последовательное включение n - счетчиков с различными модулями счета Mi. Возможна постановка двух задач. В первой необходимо определить...

-

СИНХРОННЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В синхронном счетчике импульсы поступают на тактовые входы всех триггеров одновременно. Ниже на рисунке ниже приведен трехразрядный счетчик с модулем...

-

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти...

-

СЧЕТЧИКИ - Цифровые устройства и микропроцессоры

Счетчик (Сч) - последовательностная схема, преобразующая поступающие на вход импульсы в код Q, пропорциональный их количеству. Большинство счетчиков...

-

РЕГИСТРЫ, ПАРАЛЛЕЛЬНЫЕ И ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ - Цифровые устройства и микропроцессоры

Последовательностныесхемысразличнымикомбинациямипоследовательногои параллельного способов записи и считывания информации. Выполняются на основе...

-

T - ТРИГГЕР, ВЗАИМНЫЕ ПРЕОБРАЗОВАНИЯ ТРИГГЕРОВ - Цифровые устройства и микропроцессоры

Анализ временной диаграммы при J = K = 1 (рис. 46) позволяет сделать два важных вывода. Во-первых, период повторения выходных импульсов увеличился в два...

-

D - ТРИГГЕР СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ - Цифровые устройства и микропроцессоры

D - триггер имеет два входа: информационный вход D(аtа) и вход управления записью/запоминанием (защелкиванием) L(oad)/L(atch) - отсюда его второе имя :...

-

СИНХРОННЫЙ RS - ТРИГГЕР - Цифровые устройства и микропроцессоры

Если незадействованные входы элементов И-НЕ 1 и 2 соединить вместе (рис. 36), получится синхронный RS - триггер со статическим управлением...

-

В соответствии с требованиями к ФНЧ - прототипу Баттерворта необходимо: - Определить требования к дискретному ФНЧ (ФНЧД); - Рассчитать порядок ФНЧД; -...

-

Расчет характеристик НВЛ начинается с введения исходных данных. Оно происходит следующим образом. Сначала вводится тип первого четырехполюсника (всего...

-

ПУ усиливает электрический сигнал, обеспечивая наибольшее отношение сигнал/шум. Основные требования, предъявляемые к ПУ - минимальные шумы, максимальный...

-

Условное изображение коммутационных устройств в электрических схемах - Коммутационные устройства

Настоящий стандарт распространяется на схемы, выполняемые вручную или автоматизированным способом, изделий всех отраслей промышленности и строительства и...

-

Выходной каскад для согласования с внешней нагрузкой выполнен по схеме эмиттерного повторителя. При этом RН=50 Ом и ток покоя выбирается достаточно...

-

Устройство АЦП и ЦАП - Современные звуковые карты. Методы позиционирования и сжатия звука

В основном применяется три конструкции АЦП: параллельные - входной сигнал одновременно сравнивается с эталонными уровнями набором схем сравнения...

-

Основные сведения об элементной базе устройства - Плата КП632

Устройство построено на цифровых элементах. Элемент DD1 представляет собой микросхему 133АГ3. Рис. 1.1. Микросхема К155АГ3 Микросхема К155АГ3 (рис. 1.1)...

-

Современный процесс разработки технического устройства можно разбить на следующие составные части: Научно-исследовательская работа (НИР);...

-

2.4.1 Коэффициент нестабильности задающего генератора устройства синхронизации и передатчика k=10-4. Исправляющая способность приемника µ=52%. Краевые...

-

Схемы ЭСЛ _ эмиттерно-связанной логики - Электроника и схемотехника аналоговых устройств

Цифровые микросхемы эмиттерно-связанной логики имеют более высокое быстродействие, чем схемы ТТЛ (даже ценой большей рассеиваемой мощности), достигшее в...

-

ОПЕРАТИВНЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА - Цифровые устройства и микропроцессоры

Полупроводниковые ЗУ подразделяются на ЗУ с произвольной выборкой и ЗУ с последовательным доступом. ЗУПВ подразделяются на: - статические оперативные...

-

Принципиальная схема устройства - Радиосистема пожарной сигнализации

Исходя из технических требований и структурной схемы, выберем схемы и элементную базу для устройства. В качестве генератора колебаний используем простой...

-

Теоретические основы Сигнал, поступающий с выхода канала постоянного тока (КПТ), должен быть отождествлен на приемной стороне с "0" или "1". Необходимо...

Синтез делителя частоты - Синтез дискретного устройства