Предделители таймеров/счетчиков - Таймеры-счетчики в микроконтроллерах

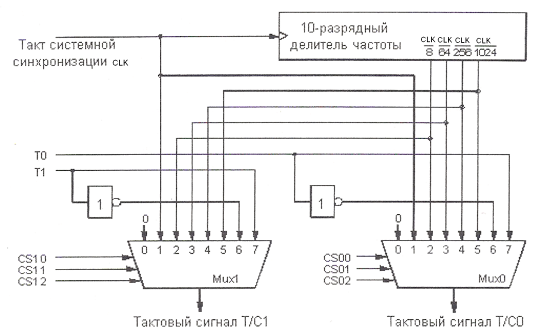

Как уже говорилось ранее, каждый таймер микроконтроллера может работать от двух разных источников тактовых импульсов. Либо это внешние импульсы, либо импульсы, вырабатываемые внутренней схемой микроконтроллера. Какой бы источник сигналов ни был выбран, перед тем, как попасть на вход таймера, этот сигнал проходит схему предварительного делителя. Предварительный делитель предназначен для того, чтобы расширить диапазон формируемых частот и длительностей таймера. Каждая микросхема АVR имеет свою структуру предварительного делителя для таймеров/счетчиков. Упрощенная схема одного из вариантов предварительного делителя приведена на рис. 5.1.

Как видно из приведенных схем, в микроконтроллеры интегрированы 10- ступенчатый делитель и мультиплексоры, осуществляющие подключение соответствующего выхода делителя ко входу счетчиков.

С выходов делителя снимаются сигналы СLК/8, CLK/64, CLK/256 и CLK/1024. В схеме имеют место цепи, через которые на вход таймера могут поступать внешние импульсы Т0 и Т1.

Рис. 1

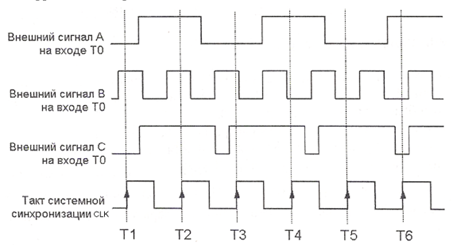

В режиме работы "Счетчик", в качестве активного фронта с помощью мультиплексора может быть выбран нисподающий или нарастающий фронт внешнего импульса на входах Т0 и Т1. При таком режиме внешний сигнал Т0 (как и Т1) синхронизируется с тактом системной синхронизации СLК внутреннего кварцевого осциллятора. Для этого внешний сигнал проверяется в течение каждого нарастающего фронта СLК (рис.).

Рис.2

На рис. 2 показаны различные сигналы, синхронизируемые сигналом CLK, при этом необходимо отметить, что только сигнал А синхронизируется без потери информации. Это необходимо учитывать при выборе частоты работы МК. автоматический микроконтроллер таймер счетчик

Все счетные сигналы поступают на входы данных мультиплексора. На адресные входы мультиплексора поступают сигналы от трех разрядов регистра управления таймером (TCCRn).

Таким образом, записывая в разряды CSn0, CSnl, CSn2 различные значения, можно выбирать один из восьми режимов работы предделителя. В зависимости от выбранного режима, на выход схемы могут поступать сигнал с одного из выходов десятиразрядного делителя, прямой сигнал с тактового генератора либо нулевой логический уровень (входа D0). В последнем случае сигнал на входе таймера будет отсутствовать, и его работа приостанавливается.

|

CSn2 |

CSn1 |

CSn0 |

Описание |

|

0 |

0 |

0 |

Источник тактирования не выбран. (Счетчик остановлен). |

|

0 |

0 |

1 |

ClkI/O/1 (Не предварительного деления). |

|

0 |

1 |

0 |

ClkI/O/8 (Тактовый сигнал с пред. делителя). |

|

0 |

1 |

1 |

ClkI/O/64 (Тактовый сигнал с пред. делителя). |

|

1 |

0 |

0 |

ClkI/O/256 (Тактовый сигнал с пред. делителя). |

|

1 |

0 |

1 |

ClkI/O/1024 (Тактовый сигнал с пред. делителя). |

|

1 |

1 |

0 |

Внешнее тактирование с вывода Tn. Такт по спадающему фронту сигнала. |

|

1 |

1 |

1 |

Внешнее тактирование с вывода Tn. Такт по нарастающему фронту сигнала. |

Здесь величиной clkI/O обозначена частота тактирования процессора.

Таким образом, схемы предделителей обеспечивают следующие восемь различных вариантов формирования счетных импульсов:

- - 0 - отсутствие импульсов; - 1 - "таймер", прямой сигнал от внутреннего генератора; - 2...5 - "таймер", один из сигналов с делителя; - 6 - "счетчик", инверсный сигнал с внешнего входа (активный ниспадающий фронт); - 7 - "счетчик", прямой внешний сигнал (активный нарастающий фронт).

Схема, приведенная на рис. 5.1, не является стандартом для всех микроконтроллеров серии АVR. Она отражает лишь общий принцип построения предделителей. В разных моделях это сделано немного по-разному.

Как уже отмечалось, способ тактирования определяется битами CSn2:0 (Clock Select), расположенными в регистре управления TCCRnB.

16-разрядный таймер/счетчик.

Более подробно рассмотрим схему таймеров/счетчиков МК ATmega 128 на примере 16-разрядного таймера/счетчика 1. Он имеет идентичную структуру с таймером/счетчиком 3.

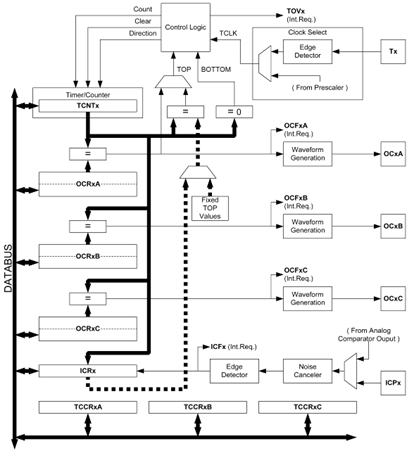

Блок-схема таймера/счетчика 1 приведена на рис. 3. Буквой "x" обозначен номер рассматриваемого таймера/счетчика (x=1).

Таймер/счетчик 1 содержит базовый счетчик TCNT1H:TCNT1L (Timer/Counter 1), имеющий шестнадцать разрядов. При поступлении тактирующего сигнала на вход схемы счетчика значение базового счетчика, в зависимости от выбранного режима работы, инкрементируется или декрементируется. Кроме того, в состав таймера-счетчика входят регистры управления TCCR1A, TCCR1B, TCCR1C (Timer/Counter 1 Control Register), два разряда регистра запросов, прерывания TIFR и столько же разрядов регистра маскирования прерываний TIMSK. Регистры TIFR и TIMSK являются общими для всех таймеров-счетчиков микроконтроллера.

Рис. 3 Блок-схема таймера/счетчика 1, 3 МК ATmega 128

Разряд регистра TIFR (Timer/Counter Interrupt Flag Register) устанавливается в единичное состояние при формировании в таймере-счетчике определенного запроса прерывания. В регистре масок прерываний TIMSK (Timer/Counter Interrupt Mask Register) устанавливаются разрешения/запрещения прерываний таймера/счетчика 1. Разряд регистра TIFR сбрасывается в нулевое состояние аппаратно при переходе микроконтроллера к выполнению соответствующей прерывающей программы или программно при выполнении команды установки бита в единичное состояние.

В состав таймера/счетчика, выполняющего функцию сравнения или ШИМ, входят регистры сравнения OCR1АH:OCR1АL, OCR1BH:OCR1BL, OCR1CH:OCR1CL (Output Compare Register), а в состав таймера/счетчика, выполняющего функцию захвата, -- регистр захвата ICR1H:ICR1L (Input Capture Register). Разрядность регистров OCR1 и ICR1 равна разрядности базового счетчика TCNT1.

16-разрядный таймер/счетчик 1 может получать тактовый сигнал от СLК, СLК после предварительного делителя и от внешнего вывода. Кроме того, его можно остановить. При внешнем тактировании таймера/счетчика 1 внешний сигнал синхронизируется частотой тактового генератора CPU.

Наилучшие точность и разрешение 16-разрядный таймер/счетчик 1 обеспечивает при наименьшем коэффициенте предварительного деления. С другой стороны, высокий коэффициент предварительного деления удобен при реализации таймером/счетчиком 1 низкоскоростных функций или точной синхронизации редко происходящих действий. Таймер/счетчик1 поддерживает функции сравнения выхода, используя регистры сравнения выходов А, В и C - OCR1А, OCR1В, OCR1C в качестве источников данных, сравниваемых с содержимым таймера/счетчика 1.

Таймер/счетчик 1 может быть использован в качестве 8, 9 или 10-разрядного широтно-импульсного модулятора. В этом режиме счетчик и регистры OCR1A/OCR1B/OCR1С работают как сдвоенный самостоятельный ШИМ со сцентрированными импульсами, без формирования ложных импульсов.

Функция захвата входа таймера/счетчика 1 обеспечивает захват содержимого таймера/счетчика 1 в регистр захвата входа, запускаемый внешним событием на выводе входа захвата IC1. Реальные установки захвата события определяются регистром управления таймером/счетчиком 1 TCCR1B. Кроме того, для переключения входа захвата может быть использован аналоговый компаратор. Если разрешена функция подавления шума, действительные условия переключения события захвата тестируются четырьмя выборками, прежде чем захват будет активирован. Тестирование сигнала на входном выводе производится с частотой тактирования ядра МК.

Похожие статьи

-

Обращение к 16-разрядным регистрам - Таймеры-счетчики в микроконтроллерах

Рассмотрим некоторые тонкости в обращении к 16-разрядным регистрам таймера/счетчика 1. Регистры TCNTn, OCRnA/B/C и ICRn - 16-разрядные и обращение к ним...

-

Базовый счетчик (Counter Unit) - Таймеры-счетчики в микроконтроллерах

Основной частью 16-разрядного таймера/счетчика 1 является реверсивный базовый счетчик TCNTn. Его блок-схема изображена на следующем рисунке 4: Рис. 4...

-

Таймеры-счетчики - Таймеры-счетчики в микроконтроллерах

Общие сведения Любой микроконтроллер серии АVR содержит несколько встроенных таймеров. Причем по своему назначению их можно разделить на две категории. К...

-

КАСКАДНОЕ ВКЛЮЧЕНИЕ СЧЕТЧИКОВ, СЧЕТЧИК - ТАЙМЕР - Цифровые устройства и микропроцессоры

Рассмотрим последовательное включение n - счетчиков с различными модулями счета Mi. Возможна постановка двух задач. В первой необходимо определить...

-

Формирователь импульсов, Счетчик импульсов - Цифровой блок управления резьбонарезным шпинделем

В качестве ФИ используем триггер Шмитта, который позволяет исключить влияние помехи и повысить крутизну фронта среза импульсов подаваемых на СИ. Так как...

-

Регистры, Счетчики - Оcновы радиоэлектроники

Регистры -- это устройства для приема, хранения и передачи информации, причем информация здесь -- это некоторое сочетание нулей и единиц. Кроме того, на...

-

РЕВЕРСИВНЫЙ СЧЕТЧИК - Цифровые устройства и микропроцессоры

Схема двухразрядного счетчика с общим входом сброса R, выходом переноса CR при суммировании и выходом переноса BR при вычитании приведена на рис. внизу....

-

СЧЕТЧИКИ - Цифровые устройства и микропроцессоры

Счетчик (Сч) - последовательностная схема, преобразующая поступающие на вход импульсы в код Q, пропорциональный их количеству. Большинство счетчиков...

-

Подсчет импульсов является одной из наиболее распространенных операций, выполняемых в устройствах дискретной обработки информации. Такая операция в...

-

АСИНХРОННЫЙ СЧЕТЧИК C ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В качестве примера возьмем четырехразрядный счетчик. Четыре двоичных разряда счетчика обеспечивают М = 16 состояний. Ниже приведена схема и условное...

-

ПРИМЕНЕНИЕ СЧЕТЧИКОВ В ИЗМЕРИТЕЛЬНОЙ ТЕХНИКЕ - Цифровые устройства и микропроцессоры

На рисунке внизу последовательно включены 6 счетчиков с модулем 10 (двоично - десятичные). Информационные выходы Qi каждого каскада через преобразователь...

-

Сброс и обработка прерываний - Программа для управления регулятором скорости вращения двигателя

В AT90S1200 предусмотрены 3 различных источника прерываний. Эти прерывания и сброс имеют различные векторы в области памяти программ. Каждое из...

-

Формирователь импульсов, Счетчик импульсов - Цифровой блок управления

Формирователь импульсов можно изготовить на основе триггера Шмитта, который имеет пороги срабатывания и отпускания, между которыми существует зона...

-

РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА - Цифровые устройства и микропроцессоры

Название указывает, что сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую. Одна из возможных схем трехразрядного...

-

Проектирование схемы тактирования АЦП. - Разработка аналого-цифрового преобразователя

Схема тактирования предназначена для подачи тактовых импульсов, а также для подачи стартового импульса на регистр последовательных приближений. Схема...

-

Расчет схемы электрической принципиальной цифрового матрицирующего устройства. Рассмотрим систему обозначений сигналов, принятую в цифровом телевидении...

-

СИНХРОННЫЙ СЧЕТЧИК С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ - Цифровые устройства и микропроцессоры

В синхронном счетчике импульсы поступают на тактовые входы всех триггеров одновременно. Ниже на рисунке ниже приведен трехразрядный счетчик с модулем...

-

Описание функциональной схемы. - Счетчик импульсов

В функциональной схеме отдельные элементы рассматриваются с точки зрения их назначения. Различные элементы могут выполнять одинаковые функции. По этому...

-

Параллельные (синхронные) счетчики с непосредственными связями характеризуются Одновременным поступлением счетного импульса на входы всех разрядов...

-

Применяя к выражению (13) аксиому двойного отрицания (9) получим: Yмажор =~(~( x2*x0 + x1*x0 + x2*x1))(14) Формуле (14) соответствует схема (рис.8,слева)...

-

В данной схеме используется импортный аналог регистра последовательных приближений К155ИР17 - микросхему фирмы AMD - АМ2504, которая работает на частоте...

-

Классификация систем синхронизации Синхронизация есть процесс установления и поддержания определенных временных соотношений между двумя и более...

-

Помимо аналого-цифровых преобразователей (АЦП), работой цифровой логики могут управлять операционные усилители (ОУ) и компараторы, преобразующие...

-

Классификация систем синхронизации Синхронизация есть процесс установления и поддержания определенных временных соотношений между двумя и более...

-

Цифровые устройства и микропроцессоры

Введение Счетчики выполняют на запоминающих элементах - триггерах. Он фиксирует число импульсов, поступивших на его вход. В интервалах между ними счетчик...

-

Описание работы модуля по принципиальной схеме. - Счетчик импульсов

Счетчик импульсов выполнен в виде встраиваемого блока. В нутрии расположены две платы - индикации и управления, которые конструктивно объединены в...

-

T - ТРИГГЕР, ВЗАИМНЫЕ ПРЕОБРАЗОВАНИЯ ТРИГГЕРОВ - Цифровые устройства и микропроцессоры

Анализ временной диаграммы при J = K = 1 (рис. 46) позволяет сделать два важных вывода. Во-первых, период повторения выходных импульсов увеличился в два...

-

СУММАТОРЫ - Цифровые устройства и микропроцессоры

Сумматор осуществляет арифметическое суммирование n-разрядных кодов X=(x(n-1),..,x0) и Y=(y(n- 1),..,y0). Правила сложения двух одноразрядных двоичных...

-

Счетчики, объединенные общей шиной RS-485, или по интерфейсу "токовая петля" на мультиплексор (например, типа МПР-16), или устройством сбора и подготовки...

-

Обоснование выбора электрической принципиальной схемы - Умножитель частоты

Выбранная структурная схема является однокольцевым УЧ. В настоящее время характеристики, указанные в техническом задании, хорошо реализуются на...

-

КТ (командный триггер) - Цифровой блок управления резьбонарезным шпинделем

Командные триггеры строятся по схеме асинхронных RS-триггеров на логических элементах "И-НЕ", которые управляются "нулями". В качестве логических...

-

Базовые понятия - Триггеры: общая характеристика

Триггер -- это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и...

-

Микросхема ES4408 - DVD-процессоры ESS ES4318, ES4408, ES4408FD

Большинство характеристик микросхемы ES4408 совпадают с соответствующими характеристиками микросхемы ES4318. В отличие от предыдущей, микросхема ES4408...

-

Разработка функциональной схемы кодера PAL - Разработка схем кодера PAL

Функциональная схема кодера приведена на рисунке 2.1. Входные регистры служат для снижения частоты дискретизации первичных сигналов трех основных цветов...

-

Измерительные генераторы - Оcновы радиоэлектроники

В измерительном генераторе частота, форма и напряжение имитируемого сигнала устанавливаются равными необходимому значению и могут перестраиваться в...

-

Описание схемы контроля на появление недопустимых входных кодов - Конструирование СВТ

Схема контроля на появление недопустимых кодов (более 1001 (2) ) и логика работы схемы представлена на рис. 2.2 и табл. 2.1. Логика работы схемы контроля...

-

ПЕРЕХОДНЫЕ ПРОЦЕССЫ В ЛОГИЧЕСКИХ СХЕМАХ - Цифровые устройства и микропроцессоры

Отличие времени задержки tзд. р. от нуля при прохождении сигнала через логическую схему может приводить к возникновению помех в выходном сигнале. Эти...

-

Программируемый контроллер прерываний КР580ВИ59 позволяет свести до минимума аппаратные затраты на реализацию системы прерываний и обеспечивает широкое...

-

Генератор тактовых импульсов должен вырабатывать прямоугольные импульсы частотой 190 Гц. В качестве токового возьмем мультивибратор на логических...

-

Преобразователь этого типа, называемый в литературе также АЦП с Поразрядным уравновешиванием , является наиболее распространенным вариантом...

Предделители таймеров/счетчиков - Таймеры-счетчики в микроконтроллерах