Операционные элементы ЭВМ - Представление и хранение информациии в ЭВМ

Операционные элементы - это устройства цифровой техники, которые выполняют некоторые микрооперации за один или несколько тактов. Эти устройства представляют набор логических устройств и / или элементы памяти. Для связи устройств используются управляемые шины.

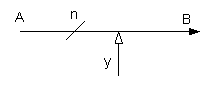

Управляемая шина - устройство для передачи цифровых кодов.

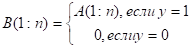

Шина - совокупность линий связи, объединенных по функциональному признаку. Передача информации может вестись, когда в каждом разряде передается только прямое или инверсное значение (однофазный код). Может быть, что передача ведется одновременно, (парафазный код).

А - источник, В-приемник, y - управляемый сигнал, n - разрядность шины

Комбинационная схема.

Классификация логических элементов:

- 1. Дешифраторы (ДШ). 6. Преобразователи кодов. 2. Шифраторы (Ш). 7. Сумматоры. 3. Мультиплексоры (МП). 8. Регистры. 4. Демультиплексоры (ДМП). 9. Счетчики. 5. Схемы сравнения кодов. 10. Схема свертки. 10. Специальные операционные элементы (встречаются редко).

Элементы с 1 по 6 могут быть реализованы в виде комбинационных схем (не содержат памяти). Элементы с 5 по 10 - автоматы (автоматы - схемы с памятью).

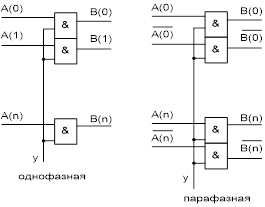

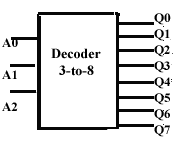

Дешифраторы (ДШ) - это устройства, которые преобразуют позиционный код в унитарный.

Унитарный код (unitary code) - двоичный код фиксированной длины, содержащий только одну "1".

ДШ преобразует входной код в номер выхода. Для построения ДШ необходимо записать конъюнкции всех наборов и реализовать их в заданном базисе.

Неполные дешифраторы - это ДШ у которых используются не все входы.

A2 |

A1 |

A0 |

Q7 |

Q6 |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Шифраторы - это устройства, которые по номеру входа выдают код.

Шифратор - логическое устройство, выполняющее преобразование позиционного кода в n-разрядный двоичный код.

Двоичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением: n=2M, где n - число входов, m - число выходных двоичных разрядов.

Изображение и таблица аналогично дешифратору.

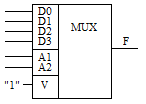

Мультиплексор - устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов. Мультиплексоры - цифровые коммутаторы каналов. МП можно использовать для реализаций логических схем. Другими словами на каждом МП можно реализовать сложную булеву функцию (одну). При этом если m адресных входов, то можно организовать функцию m+2 переменных. Переменные подаются на адресный вход.

Мультиплексор - совокупность управляемых шин с общим выходом

|

A2 |

A1 |

F |

|

0 |

0 |

D0 |

|

0 |

1 |

D1 |

|

1 |

0 |

D2 |

|

1 |

1 |

D3 |

D0..D3 - информационные входы, A1, A2 - управляющие входы

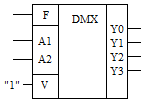

Демультиплексор - устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры - цифровые разделители каналов.

Задавая адреса, мы выбираем канал, который подключится на выход.

ДМП не выпускаются в виде отдельных схем. Они выпускаются с ДШ.

ДМП можно использовать для преобразования последовательного когда в параллельный.

|

A2 |

A1 |

Y3 |

Y2 |

Y1 |

Y0 |

|

0 |

0 |

0 |

0 |

0 |

F |

|

0 |

1 |

0 |

0 |

F |

0 |

|

1 |

0 |

0 |

F |

0 |

0 |

|

1 |

1 |

F |

0 |

0 |

0 |

Демультиплексор

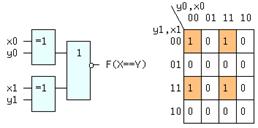

Схемы сравнения кодов. Два кода X и Y считаются равными, если попарно равны их одноименные разряды. Можно ввести функцию F (X==Y), которая равна 1, если xi=yi для всех i, иначе ее значение равно нулю. В качестве примера возьмем два двухбитовых числа X=(x1, x0) и Y=(y1, y0).

Практические схемы дополняются функциями "больше / меньше", как например в микросхеме 555СП1, которая сравнивает два четырехразрядных числа. Схема сравнения входит в состав АЛУ микропроцессора и часто называется цифровым компаратором.

Преобразователи кодов. Это группа элементов, которая преобразует один тип кода в другой. Что бы построить преобразователь кодов, необходимо составить таблицу истинности для входного и выходного кодов. Затем провести совместную минимизацию системы булевых функций для всех выходов. Затем уравнения переводятся в требуемый базис и реализуются.

Под преобразованием кодов понимается преобразование n-разрядных двоичных чисел, представляющих информацию в одном заданном коде, в m-разрядные двоичные числа, представляющие эту информацию в другом коде. Наиболее распространены следующие два подхода к построению преобразователей кодов.

Первый подход - синтез m независимых одновыходных функций по заданной таблице истинности - таблице соответствия кодов.

Допустим, имеется таблица истинности преобразователя 2-х разрядного двоичного кода в 3-х разрядный:

|

A1 |

A0 |

B2 |

B1 |

B0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

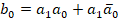

Считая b0, b1 и b2 независимыми одновыходными функциями, запишем для каждой из них булевые выражения. ; ;

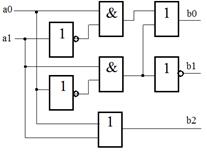

Используя приведенные булевы выражения с учетом того, что инверсии некоторых переменных и произведение встречаются не в одной функции, составляем схему преобразователя с применением (где это возможно) одних и тех же логических элементов:

A |

B |

|

0 |

4 |

|

1 |

1 |

|

2 |

3 |

|

3 |

0 |

Второй подход - построение преобразователя кодов по методу "дешифратор-шифратор".

В этом случае по заданной таблице истинности составляется таблица соответствия десятичных цифр. В рассмотренном примере эта таблица запишется следующим образом

Метод построения преобразователя заключается в следующем.

Сначала строится схема преобразователя двоичного кода в унарный, т. е. такой код, когда "1" может быть только на одном из N выходов преобразователя, номер которого совпадает с числом, представленным входным двоичным кодом, (такой преобразователь называется дешифратором). Число выходов дешифратора равно N = 2n, где n - число разрядов входного кода дешифратора.

Затем строится схема преобразователя, осуществляющего обратную операцию, т. е. преобразование унарного кода в двоичный. Число входов такого преобразователя, который называется шифратором, равно M = 2m, где m - число разрядов выходного кода шифратора.

Схема преобразователя кода образуется соединением выходов дешифратора и входов шифратора в соответствии с таблицей соответствия десятичных цифр. Здесь DC - обозначение дешифратора (DECODER), CD - обозначение шифратора (ENCODER).

Сумматор - устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов

В зависимости от способа ввода разрядов слагаемых сумматоры делятся на два типа: последовательного и параллельного действия. В сумматоры первого типа разряды чисел вводятся в последовательной форме, т. е. разряд за разрядом (младшим разрядом вперед), в сумматоры второго типа каждое из слагаемых подается в параллельной форме, т. е. одновременно всеми разрядами.

Сумматор последовательного действия. Состоит из одноразрядного сумматора, выход pi+1 которого соединен с входом pi через элемент задержки, параметры которого согласованы со скоростью поступления разрядов слагаемых на входы сумматора. Операция суммирования во всех разрядах слагаемых осуществляется с помощью одного и того же одноразрядного сумматора, но последовательно во времени, начиная с младших разрядов. Такое построение сумматора возможно за счет того, что слагаемые поступают в последовательной форме.

Достоинство сумматора последовательного действия заключается в малом объеме оборудования, требуемого для его построения. Однако в связи с необходимостью последовательной обработке разрядов приводит к низкому быстродействию.

Сумматор параллельного действия. Состоит из отдельных разрядов, каждый из которых содержит одноразрядный сумматор.

При подаче слагаемых цифры их разрядов поступают на соответствующие одноразрядные сумматоры. Каждый из одноразрядных сумматоров формирует на своих выходах цифру соответствующего разряда суммы и перенос, передаваемый на вход одноразрядного сумматора следующего (более старшего) разряда. Такая организация процесса переноса, называемая последовательным переносом, снижает быстродействие многоразрядных сумматоров, т. к. получение результата в старшем разряде сумматора обеспечивается только после завершения распространения переноса по всем разрядам.

Регистры - последовательное логическое устройство, используемое для хранения n-разрядных двоичных слов (чисел) и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств.

Регистром называется функциональный узел, осуществляющий прием, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. По типу приема и выдачи информации различают 3 типа регистров:

- - С последовательным приемом и выдачей информации - сдвиговые регистры. - С параллельным приемом и выдачей информации - параллельные регистры. - С параллельно-последовательным приемом и выдачей информации

Сдвиговые регистры представляют собой последовательно соединенную цепочку триггеров. Основной режим работы - сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала.

Параллельно-последовательный:

- - Ввод осуществляется параллельно - Вывод последовательно

Счетчики. Счетчик числа импульсов - устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счетчики могут строиться на T-триггерах. Основной параметр счетчика - модуль счета - максимальное число единичных сигналов, которое может быть сосчитано счетчиком. Счетчики обозначают через СТ (от англ. counter).

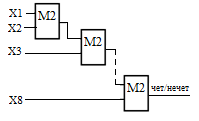

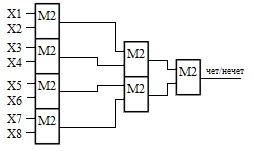

Схема свертки - контроль на нечет.

Над пересылаемым словом выполняется операция свертки. Если результат равен 1, то он дополняется контрольным разрядом 1. Позволяет обнаружить все нечетные ошибки.

Линейная схема Пирамидальная схема

Похожие статьи

-

Арифметические операции в двоичной системе счисления Умножение в двоичной системе счисления = поразрядные сдвиги + суммирование Основные форматы хранения...

-

Представление информации в ЭВМ - Представление и хранение информациии в ЭВМ

В большинстве ЭВМ информация представляется в двоичном виде (Существуют так же двоично-десятичные и троичные ЭВМ). Это обусловлено, в основном,...

-

Контроль функционирования ЭВМ - Представление и хранение информациии в ЭВМ

Назначение схем контроля цифровых устройств, виды контроля для комбинационных схем Потери времени в таких сложных объектах, как ЭВМ, в первую очередь...

-

Машинная арифметика с плавающей точкой - Представление и хранение информациии в ЭВМ

Число с плавающей точкой: X=±Mx-S±px Здесь: M - мантисса; S - порядок. 0.314 101 0.0314 102 Машинные числа. Машинными называются числа, допускающие...

-

Интерфейсы систем управления. Классификация, основные характеристики интерфейсов. Системные (внутримашинные) интерфейсы. Интерфейсы персональных...

-

Интересной особенностью блока питания принтера Epson DFX-8000 является наличие схемы, контролирующей уровень первичного напряжения. Схема состоит из...

-

Основным преобразователем формируются напряжения: +5В для питания всей электронной части принтера и цифровых микросхем; +12В для питания цепей...

-

Представляет собой двухтактный импульсный преобразователь, силовыми ключами которого являются Q1 и Q2. При поочередном переключении этих транзисторов...

-

Датчики. Назначение, основные типы датчиков и физические принципы действия. Датчики механических величин (линейных и угловых перемещений, скорости,...

-

Для реализации устройства управления потребуются: генератор слов, логические элементы (И, ИЛИ, НЕ), счетчики и логический анализатор. Ниже приведены...

-

Интеграмльная (микро) схемма (ИС, ИМС, м/сх, англ. Integrated circuit, IC, microcircuit, microchip, silicon chip, chip), чип, микрочимп - тонкая...

-

Уже пакетный режим в своем развитом варианте требует разделения процессорного времени между выполнением нескольких программ. Необходимость в разделении...

-

Существуют две группы определений ОС: "совокупность программ, управляющих оборудованием" и "совокупность программ, управляющих другими программами". Обе...

-

Устойчивость элементов и устройств к внешним воздействиям. Характеристики климатических воздействий. Механическая прочность. Радиационная стойкость...

-

Входные фильтры имеют самое обычно построение, за исключением того, что установлены два каскада фильтров подряд, что обеспечивает более качественную...

-

Каждая СУБД имеет особенности в представлении структуры таблиц, связей, определении типов данных и т. д. которую необходимо учитывать при проектировании....

-

Элементы и устройства автоматики

2 лекция. Типовые структуры и средства АСУ ТП. Локальные системы контроля, регулирования и управления. Автоматизированные системы управления...

-

Метод представления знаний при проектировании модели - Искусственный интеллект

Предлагаемая модель ИИ основывается на когнитивных картах - некотором базовом знании о мире. Ключевые идеи, положенные в основу этой концепции, сходны с...

-

Дисковые разделы, MBR, загрузочные сектора и таблица разделов - Операционная система Linux

Весь жесткий диск может быть разбит на несколько разделов, причем каждый раздел представлен так, как если бы это был отдельный диск. Разделение...

-

Для третьего способа мне понадобился способ под названием "Стемминг". Данное понятие очень популярно во всемирной паутине, так как оно применяется в...

-

Основная статья: Операционная система реального времени Применение универсальных компьютеров для управления производственными процессами потребовало...

-

ИЕРАРХИЧЕСКАЯ МОДЕЛЬ ДАННЫХ ИМД основана на понятии деревьев, состоящих из вершин и ребер. Вершине дерева ставится в соответствие совокупности атрибутов...

-

Предшественником ОС следует считать служебные программы (загрузчики и мониторы), а также библиотеки часто используемых подпрограмм, начавшие...

-

Операционная система - Программное обеспечение информационных компьютерных систем

Операционная система - это комплекс взаимосвязанных системных программ, назначение которого - организовать взаимодействие пользователя с компьютером и...

-

Системы счисления. Представление данных в ЭВМ - Основы программирования

В современном мире для записи числовой информации используют позиционные системы счисления, в которых числа записываются с помощью ограниченного...

-

Типы разделов - Операционная система Linux

Таблицы разделов (одна находится в MBR, другие используются для расширенных разделов) содержат один байт для каждого раздела, который указывает тип...

-

Кодирование информации -- процесс преобразования сигнала из формы, удобной для непосредственного использования информации, в форму, удобную для передачи,...

-

Хранение, кодирование и пpеобpазование данных - Единицы измерения информации в памяти ПК

Хранение информации в памяти ЭВМ - одна из основных функций компьютера. Любая информация хранится с использованием особой символьной формы, которая...

-

Физические модели хранения данных определяют методы размещения данных в памяти компьютера или на соответствующих носителях информации, а также способы...

-

Формы - Проблема организации и хранения данных

Работа с данными в режиме таблицы имеет существенный недостаток: если полей слишком много, они не умещаются на экране и приходится прибегать к различным...

-

Разработка элементов интеллектуальных систем с использованием логической модели представления знаний

Разработка элементов интеллектуальных систем с использованием логической модели представления знаний 1. Задание 1 Цель - Знакомство с основами...

-

YAFFS ( Yet Another Flash File System ) - YAFFS - это первая файловая система, разработанная специально для использования на NAND накопителях. Автором...

-

Назначение и функции программной системы Разработанная база данных "Библиотека" предназначена для использования в учреждениях библиотек. Основной...

-

Гибкие диски - Операционная система Linux

Гибкий диск состоит из мягкой пластины, покрытой с одной или обоих сторон материалом, подобным тому, которым покрыты пластины в жестком диске. У самой...

-

Преимущества и недостатки Windows - Операционная система Windows

Преимущества. Удобство и поддержка устройств. Основное отличие программ для DOS и для Windows состоит в том, что DOS-программа может работать с...

-

Поиск, сбор и хранение научной информации - Поиск, накопление и обработка информации

Не все окружающие нас источники информации можно использовать для подготовки научных работ. Ведь научная работа всегда имеет достаточно узкую...

-

Способы представления звука в цифровом виде - Разработка системы регистрации новых пользователей

Исходная форма звукового сигнала - непрерывное изменение амплитуды во времени - представляется в цифровой форме с помощью "перекрестной дискретизации" -...

-

Программные модули проекта, Представление графа в памяти ЭВМ - Алгоритмы нескольких махов

Все программы были реализованы на языке С++ на персональной ЭВМ с операционной системой Windows. Каждая программа представляет собой консольное...

-

Отличия цифрового представления сигналов от аналогового Традиционное аналоговое представление сигналов основано на подобии (аналогичности) электрических...

-

Базовые понятия информации - Компьютерные и сетевые технологии

Информация компьютер математический сеть Мы начинаем первое знакомство с величайшим достижением нашей цивилизации, стоящем в одном ряду с изобретением...

Операционные элементы ЭВМ - Представление и хранение информациии в ЭВМ