Что происходит во время записи? - Компьютерные и сетевые технологии

При обращениях к кэш-памяти на реальных программах преобладают обращения по чтению. Все обращения за командами являются обращениями по чтению и большинство команд не пишут в память. Обычно операции записи составляют менее 10% общего трафика памяти. К счастью, общий случай является и более простым. Блок из кэш-памяти может быть прочитан в то же самое время, когда читается и сравнивается его тэг. Таким образом, чтение блока начинается сразу как только становится доступным адрес блока. Если чтение происходит с попаданием, то блок немедленно направляется в процессор. Если же происходит промах, то от заранее считанного блока нет никакой пользы, правда нет и никакого вреда.

Однако при выполнении операции записи ситуация коренным образом меняется. Именно процессор определяет размер записи (обычно от 1 до 8 байтов) и только эта часть блока может быть изменена. В общем случае это подразумевает выполнение над блоком последовательности операций чтение - модификация - запись: чтение оригинала блока, модификацию его части и запись нового значения блока. Более того, модификация блока не может начинаться до тех пор, пока проверяется тэг, чтобы убедиться в том, что обращение является попаданием. Поскольку проверка тэгов не может выполняться параллельно с другой работой, то операции записи отнимают больше времени, чем операции чтения.

Очень часто организация кэш-памяти в разных машинах отличается именно стратегией выполнения записи. Когда выполняется запись в кэш-память имеются две базовые возможности: сквозная запись (write through, store through) - информация записывается в два места: в блок кэш-памяти и в блок более низкого уровня памяти; запись с обратным копированием (write back, copy back, store in) - информация записывается только в блок кэш-памяти. Модифицированный блок кэш-памяти переписывается в основную память только тогда, когда он замещается. Для сокращения частоты копирования блоков при замещении обычно с каждым блоком кэш-памяти связывается так называемый бит модификации (dirty bit). Этот бит состояния показывает был ли модифицирован блок, находящийся в кэш-памяти. Если он не модифицировался, то обратное копирование отменяется, поскольку более низкий уровень содержит ту же самую информацию, что и кэш-память.

Оба подхода к организации записи имеют свои преимущества и недостатки. При записи с обратным копированием операции записи выполняются со скоростью кэш-памяти, и несколько записей в один и тот же блок требуют только одной записи в память более низкого уровня. Поскольку в этом случае обращения к основной памяти происходят реже, вообще говоря, требуется меньшая полоса пропускания памяти, что очень привлекательно для мультипроцессорных систем. При сквозной записи промахи по чтению не влияют на записи в более высокий уровень, и, кроме того, сквозная запись проще для реализации, чем запись с обратным копированием. Сквозная запись имеет также преимущество в том, что основная память имеет наиболее свежую копию данных. Это важно в мультипроцессорных системах, а также для организации ввода/вывода.

Обычно в кэш-памяти, реализующей запись с обратным копированием, используется размещение записи в кэш-памяти (в надежде, что последующая запись в этот блок будет перехвачена), а в кэш-памяти со сквозной записью размещение записи в кэш-памяти часто не используется (поскольку последующая запись в этот блок все равно пойдет в память).

Разновидности строения кэш-памяти

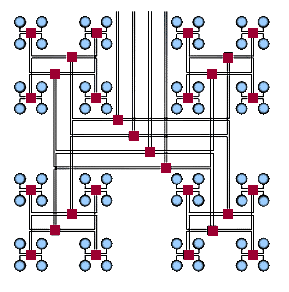

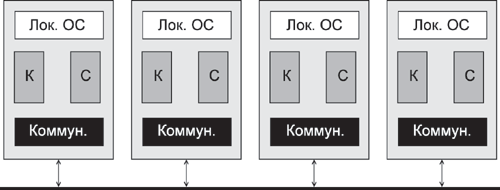

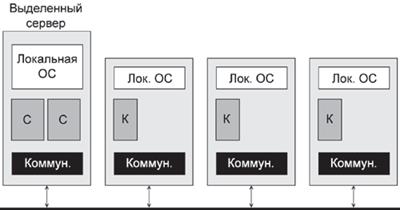

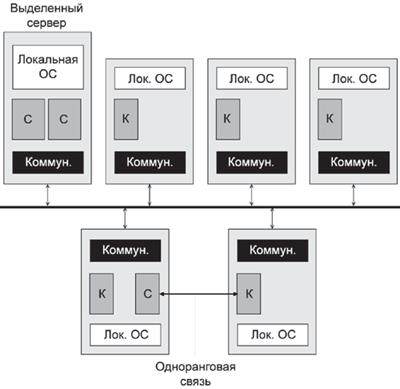

Одним из основных вопросов увеличения эффективности кэш-памяти является следующий: должны ли команды и данные находится вместе в общей кэш-памяти. Очевидно, разработать смежную кэш-память, в которой хранятся и данные и команды проще. При этом вызов команд и данных автоматически уравновешивается. Тем не менее в настоящее время преобладает тенденция к применению разделенной кэш-памяти, когда команды хранятся в одной кэш-памяти, а данные в другой. Существует три основных способа организации кэш-памяти:

В первом случае (а) кэш хранит как команды, так и адреса, а во втором случае (в) кэши разделены, но шина для данных и для команд одна общая (однофазная Гарвардская архитектура). Есть еще и третья возможность - полная Гарвардская архитектура (с), которая подразумевает не только хранение данных и команд в двух раздельных кэшах, но и наличие полностью раздельных шин. Разделенная кэш-память позволяет осуществлять параллельный доступ и к данным, и к операндам. К тому же, поскольку команды обычно не меняются во время исполнения программы, содержание командной кэш-памяти не приходится переписывать обратно в ОП.

После процессора i486, в процессорах Pentium используется раздельная кэш-память команд и данных емкостью по 8-16 Кбайт, что обеспечивает независимость обращений. За один такт из каждой кэш-памяти могут считываться два слова. При этом кэш-память данных построена на принципах двух кратного расслоения, что обеспечивает одновременное считывание двух слов, принадлежащих одной строке кэш-памяти. Для повышения эффективности перезагрузки кэш-памяти в процессоре применяется 64-битовая внешняя шина данных. В настоящее время между разделенной кэш-памятью первого уровня помещается кэш второго уровня и, даже, третьего уровня. Мы уже упоминали что наличие кэш-памяти существенно ограничивает полезную площадь кристалла (Alpha 21164 компании Digital имеет 50% площади кристалла под кэш), но это не вся правда. Для производительной работы кэша необходимы эффективные алгоритмы внеочередного и спекулятивного выполнения (выборки) команд. А это, в свою очередь, приводит к неоправданному усложнению архитектуры процессора. Сравните: процессор MIPS R5000 - простой RISC процессор, процессор MIPS R10000 - сложный CPU со всеми возможностями спекулятивного выполнения выборки и исполнения команд. Производительность его всего лишь на 1,6 раза выше, чем у R5000 , зато площадь больше в 3,4 раза. В последнее время идут интенсивные работы по интегрированию на кристалле динамической памяти с произвольной выборкой (DRAM) вместо кэшей на SRAM. Это направление получило название интеллектуальной памяти - IRAM. Интегрированная на кристалл оперативная память занимает такую же площадь, что и кэш SRAM, но способна вместить в 30-40 раз больше данных.

Память является важнейшим ресурсом, требующим тщательного управления со стороны мультипрограммной операционной системы. Распределению подлежит вся оперативная память, не занятая операционной системой. Обычно ОС располагается в самых младших адресах, однако может занимать и самые старшие адреса. Функциями ОС по управлению памятью являются: отслеживание свободной и занятой памяти, выделение памяти процессам и освобождение памяти при завершении процессов; вытеснение процессов из оперативной памяти на диск, когда размеры основной памяти не достаточны для размещения в ней всех процессов, и возвращение их в оперативную память, когда в ней освобождается место; а также настройка адресов программы на конкретную область физической памяти. Все выше перечисленное относится к логической организации памяти.

Выводы

Память - это одно из основных устройств ЭВМ, которое служит для хранения программ и данных.

Память ЭВМ - это совокупность всех запоминающих устройств, входящих в состав машины.

Память компьютера - система иерархическая, состоящая из нескольких уровней.

Внутренняя память может строиться на самых разнообразных физических принципах, но по своему функциональному назначению различается на ОЗУ, ПЗУ, ППЗУ и др.

Современные ОЗУ изготавливаются в виде полупроводниковых микросхем двух типов - статических и динамических.

Для разрешения проблемы соответствия времени обработки данных в процессоре и времени обращения к ОП применяется структура многоуровневого буфера - кэш-память.

В современных компьютерах кэш-память обычно реализуется по двух и трехуровневой схеме. При этом кэш 1-го уровня выполняется непосредственно на кристалле процессора, а кэш 2-го уровня (3-го) устанавливается на системной плате.

Память является важнейшим ресурсом, требующим тщательного управления со стороны мультипрограммной операционной системы.

Вопросы и задания

Как соотносятся между собой объем памяти и ее быстродействие и почему?

Что хранится в ПЗУ компьютера?

Что такое BIOS и каковы его функции?

Перечислите достоинства и недостатки статических и динамических МС.

Что такое кэш-память и как она работает?

Можно ли считать из памяти отдельно взятый бит?

Оцените, какая доля адресного пространства памяти вашего компьютера реально занята.

Лекция 8. Логическая организация памяти

Мы уже говорили, что размер реальной физической памяти не соответствует адресному пространству процессора, разрядности его адресной шины. Эта проблема всегда актуальна, а ранее она была просто угрожающей. Программисты тратили много времени на то, что бы впихнуть свои программы в небольшую основную память процессора.

Существовала еще одна проблема, аппаратная организация памяти в виде линейного набора ячеек не соответствует представлениям программиста о том, как организовано хранение программ и данных. Большинство программ представляет собой набор модулей, созданных независимо друг от друга. Иногда все модули, входящие в состав процесса, располагаются в памяти один за другим, образуя линейное пространство адресов. Однако чаще модули помещаются в разные области памяти и используются по-разному.

Виртуальная память

Эти проблемы решались и решаются до сих пор. Есть несколько способов, позволяющих согласовать разные объемы памяти, разные способы ее организации в представлении программистов и реально аппаратно существующей.

Традиционным решением было использование вспомогательной памяти и разделения программы на несколько частей, так называемых оверлеев, каждый из которых перемещался по мере надобности между основной и вспомогательной памятью. В дальнейшем этот метод развился в страничную организацию памяти, когда память разбивалась на блоки фиксированного объема - страницы. Именно они образовывали единое линейное пространство адресов и перемещались с диска на основную память. Однако и этот метод не вполне удовлетворил потребности программистов и эволюционировал в сегментную организацию памяти. Сегмент - область памяти определенного назначения, внутри которой поддерживается линейная адресация. В этом случае память представлялась блоками переменной длины (и большего размера, по отношению к страницам) - сегментами, иногда их называют параграфами что, на мой взгляд, больше отвечает существу дела.

Развитие методов организации вычислительного процесса в этом направлении привело к появлению метода, известного под названием - виртуальная память, о чем мы будем говорить более подробно ниже.

Таким образом, виртуальная память - это совокупность программно-аппаратных средств, позволяющих пользователям писать программы, размер которых превосходит имеющуюся оперативную память; для этого виртуальная память решает следующие задачи:

Размещает данные в запоминающих устройствах разного типа, например, часть программы в оперативной памяти, а часть на диске;

Перемещает по мере необходимости данные между запоминающими устройствами разного типа, например, подгружает нужную часть программы с диска в оперативную память;

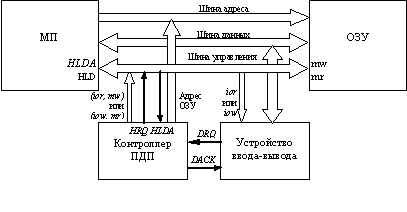

Все эти действия выполняются автоматически, без участия программиста, то есть механизм виртуальной памяти является прозрачным по отношению к пользователю. Трансляцию виртуальных адресов в физические выполняет модуль управления памятью или же диспетчер памяти (Memory Management Unit). Когда нужные данные (или команды) отсутствуют в основой памяти, диспетчер перемещает их туда с диска, для этого используется механизм ПДП. Наиболее распространенными реализациями виртуальной памяти является страничное, сегментное и странично - сегментное распределение памяти, а также свопинг.

Страничная организация памяти

О несоответствии адресного пространства логической памяти реальному объему физической памяти мы уже говорили. Теперь посмотрим, как это противоречие преодолевается в современных процессорах, но начнем с более простого примера.

Пусть наш компьютер имеет 16-битное поле адреса и всего лишь 4096 слов оперативной памяти (PDP-1). Программа, работающая на нем, могла бы обращаться к 65536 словам (216=65536), но такого количества слов просто нет. До изобретения виртуальной памяти все адреса, которые были равны или больше адреса 4096 считались бесполезными, не существующими.

Идея разделения понятий адресного пространства и адресов памяти состоит в следующем. В любой момент времени можно получить прямой доступ к 4096 словам памяти, но это не значит, что они непременно должны соответствовать адресам от 0 до 4095. Например, мы могли бы сообщить компьютеру, что при обращении к адресу 4096 должно использоваться слово из памяти с адресом 0, при обращении к адресу 4097 - слово с адресом 1, а при обращении к адресу 8191 - слово с адресом 4095 и т. д. Другими словами, мы отобразили логическое адресное пространство на действительные адреса физической памяти (рис.7.9)

Возникает вопрос: а что произойдет, если программа совершит переход в один из адресов с 8192 по 12287? В машине без виртуальной памяти на экране появится фраза "Несуществующий адрес памяти" и выполнение программы остановится. В машине с виртуальной памятью будет иметь следующая последовательность действий:

Слова с 4096 до 8191 будут выгружены на диск.

Слова с 8102 до 12287 будут загружены с диска в основную память.

Отображение адресов изменится: теперь адреса с 8192 до 12287 соответствуют ячейкам памяти с 0 по 4095.

Выполнение программы продолжится.

Если теперь добавить в основную память еще три блока по 4 К, то мы сможемм отобразить полностью 64 К адресного пространства на всего лишь 4К физической памяти. Такая технология автоматического наложения называется страничной организацией памяти, а куски программы, которые считываются с диска, называются страницами. Необходимо подчеркнуть, что страничная организация памяти создает иллюзию большой линейной основной памяти такого же размера, как адресное пространство. Программист может писать программы и при этом ничего не знать о существовании страничной организации памяти, этот механизм называют прозрачным.

Страничное управление памятью - это общепринятый механизм организации виртуальной памяти с подкачкой страниц по запросу. Страничная трансляция адресов выполняется блоком управления памятью (Memory Management Unit - MMU), расположенным в процессоре, с использованием каталогов и таблиц дескрипторов страниц - структур в физической ОП. Блок MMU делит линейный адрес на виртуальные страницы фиксированного размера (4К, 4М, 2М). На такие же страницы делится и адресное пространство физических адресов.

Преобразование адресов

Приведем пример страничного распределения памяти. Виртуальное адресное пространство каждого процесса делится на части одинакового, фиксированного для данной системы размера, называемые виртуальными страницами. В общем случае размер виртуального адресного пространства не является кратным размеру страницы, поэтому последняя страница каждого процесса дополняется фиктивной областью. Вся оперативная память машины также делится на части такого же размера, называемые физическими страницами (или блоками). Размер страницы обычно выбирается равным степени двойки: 512, 1024 и т. д., это позволяет упростить механизм преобразования адресов. При загрузке процесса часть его виртуальных страниц помещается в оперативную память, а остальные - на диск. Смежные виртуальные страницы не обязательно располагаются в смежных физических страницах. При загрузке операционная система создает для каждого процесса информационную структуру - таблицу страниц, в которой устанавливается соответствие между номерами виртуальных и физических страниц для страниц, загруженных в оперативную память, или делается отметка о том, что виртуальная страница выгружена на диск. Кроме того, в таблице страниц содержится управляющая информация, такая как признак модификации страницы, признак невыгружаемости (выгрузка некоторых страниц может быть запрещена), признак обращения к странице (используется для подсчета числа обращений за определенный период времени) и другие данные, формируемые и используемые механизмом виртуальной памяти.

Базовый регистр Сгенерированный процессором

Таблицы страниц виртуальный адрес

При активизации очередного процесса в специальный регистр процессора загружается адрес таблицы страниц данного процесса. При каждом обращении к памяти происходит чтение из таблицы страниц информации о виртуальной странице, к которой произошло обращение. Если данная виртуальная страница находится в оперативной памяти, то выполняется преобразование виртуального адреса в физический. Если же нужная виртуальная страница в данный момент выгружена на диск, то происходит так называемое страничное прерывание. Выполняющийся процесс переводится в состояние ожидания, и активизируется другой процесс из очереди готовых. Параллельно программа обработки страничного прерывания находит на диске требуемую виртуальную страницу и пытается загрузить ее в оперативную память. Если в памяти имеется свободная физическая страница, то загрузка выполняется немедленно, если же свободных страниц нет, то решается вопрос, какую страницу следует выгрузить из оперативной памяти.

Сегментная организация памяти.

Память может логически организовываться в виде одного или множества блоков, сегментов произвольной длины (в реальном режиме фиксированной). Мы уже говорили, что в защищенном режиме возможно разбиение логической памяти на страницы размером 4 Кбайт (до 5 Мбайт в современных процессорах), каждая из которых может отображаться на любую область физической памяти. Сегментация и страничная трансляция адресов могут применяться совместно и по отдельности. Сегментация является средством организации логической памяти на прикладном уровне, а страничная трансляция адресов на системном уровне.

Что бы лучше понять принцип сегментирования рассмотрим его на примере процессора Intel 8086. Вся память системы представляется не в виде непрерывного пространства, а в виде нескольких блоков -- сегментов заданного размера (по 64 Кбайт), положение которых в пространстве памяти можно изменять программным путем. Для хранения кодов адресов памяти используются не отдельные регистры, а пары регистров:

Сегментный регистр определяет адрес начала сегмента (база сегмента), то есть положение сегмента в памяти;

Регистр указателя (регистр смещения) определяет положение рабочего адреса внутри сегмента.

При этом физический 20-разрядный адрес памяти, выставляемый на внешнюю шину адреса, образуется путем сложения смещения, и адреса сегмента со сдвигом на 4 бита. Сегмент может начинаться только на 16-байтной границе памяти (так как адрес начала сегмента, по сути, имеет четыре младших нулевых разряда, то есть с адреса, кратного 16. Эти допустимые границы сегментов называются границами параграфов. Отметим, что введение сегментирования, прежде всего, связано с тем, что внутренние регистры процессора 16-разрядные, а физический адрес памяти 20-разрядный (16-разрядный адрес позволяет использовать память только в 64 Кбайт, что явно недостаточно).

Чтобы лучше понять, как из двух 16 битовых слов получается 20 битовый адрес еще раз покажем это на двоичном примере.

Пусть имеется 2 машинных слова:

ABCD H и 1234 H

(вспомним, что каждая 16-ричная цифра представляет 4 бита, например - 11112 = 1510 = F16); Берем первое число и приписываем 0 справа (если больше нравится - умножаем на 16), получим ABCD0, т. е. первоначальное число, но со смещением на один 16-ричный разряд. Это 20-ти разрядное число, но оно не может нам служить 20 битовым адресом, т. к. оно заканчивается на нуль и, следовательно, может представлять только адреса которые тоже заканчиваются на нуль. Другими словами оно пригодно для адресации каждого 16-го байта или сегмента.

A*164 + B*163 + C*162 + D*161 + 0*160

При изменении A, B,C, D изменяется дискретно сегмент (параграф).

Чтобы получить окончательную схему сегментированной адресации возьмем другое 16-ти битовое число - 1234 H и сложим его с модифицированным первым:

Получим ACF04 двадцати битовое число, которое может принимать любые значения от 0 до 1 048 577

Таким образом, ABCD0 - сегментная часть, которая указывает на ту область адреса которая кратна 16 (сегмент, параграф). Второе число 1234 - смещение, которое указывает конкретное расположение байта внутри сегментного параграфа (это дает 65536 или 64 Кбайт адресов внутри сегмента). Поскольку эти составляющие перекрываются, конечный адрес можно получить различными способами:

Отметим, что линейный адрес является пятиразрядным, хотя мы использовали для сегмента и смещения четырехразрядные числа. Можно констатировать, что вычисление сегментированного адреса основано на так называемом сегментном сложении, позволяющем получить (например) 20-битовое двоичное число из двух 16 битовых.

Таким образом, мы смогли адресоваться к каждой ячейке 64 Кбайтового блока из почти 1 Мбайт объема общей памяти, используя только 16 разрядную шину адреса, а не 20 разрядную, как это было бы в случае прямой адресации.

Для обращения к нужной ячейке памяти надо задать базу сегмента и 16-битное расстояние от базы называемое смещением или относительным адресом. Преобразование пары сегмент/смещение (наз. также виртуальным адресом) в физический адрес довольно простое: пусть регистр DS содержит 1234H, а регистр SI содержит 5678H, тогда физический адрес в команде MOV AX (загрузить слово в регистр AX) будет

DSx16 + SI = 12340H + 5678H = 179B8H

Базовые адреса четырех одновременно доступных программе сегментов находятся в сегментных регистрах:

Регистр команд - CS;

Регистр данных - DS;

Стека - SS

Регистр дополнительных данных - ES.

Каждый из них 16-ти битовый, но можно считать, что они 20-ти разрядные.

Обратите внимание на магическую цифру 64 Кбайт, это объем памяти внутри которого адресация осуществляется с помощью неизменного значения сегментного регистра, т. е. внутри сегмента реализуется линейно адресуемая память.

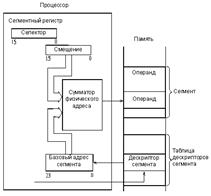

Применяются и более сложные методы сегментирования памяти. Например, в процессоре Intel 80286 в так называемом защищенном режиме адрес памяти вычисляется в соответствии с рис. 7.7. В сегментном регистре в данном случае хранится не базовый (начальный) адрес сегментов, а коды селекторов, определяющие адреса в памяти, по которым хранятся дескрипторы (то есть описатели) сегментов. Область памяти с дескрипторами называется таблицей дескрипторов. Каждый дескриптор сегмента содержит базовый адрес сегмента, размер сегмента (от 1 до 64 Кбайт) и его атрибуты. Базовый адрес сегмента имеет разрядность 24 бит, что обеспечивает адресацию 16 Мбайт физической памяти.

Рис. 8.5 Адресация памяти в защищенном режиме процессора Intel 80286.

Таким образом, на сумматор, вычисляющий физический адрес памяти, подается не содержимое сегментного регистра, как в предыдущем случае, а базовый адрес сегмента из таблицы дескрипторов.

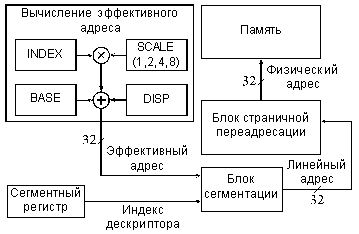

Еще более сложный метод адресации памяти с сегментированием использован в процессоре Intel 80386 и в более поздних моделях процессоров фирмы Intel. Этот метод иллюстрируется рис. 7.8. Адрес памяти (физический адрес) вычисляется в три этапа. Сначала вычисляется так называемый эффективный адрес EA (32-разрядный) путем суммирования трех компонентов: базы, индекса и смещения (Base, Index, Displacement), причем возможно умножение индекса на масштаб (Scale). Эти компоненты имеют следующий смысл:

EA = BASE + (INDEX*SCALE) + DISPLACEMENT

Здесь BASE - базовый адрес массива, INDEX - номер элемента, DISPLACEMENT - смещение внутри элемента. Массив может состоять из байтов, слов, двойных слов и учетверенных слов - это учитывается коэффициентом SCALE (1,2,34 или 8).

Рис. 8.6 Формирование физического адреса памяти процессора 80386 в защищенном режиме.

Смещение -- это 8-, 16- или 32-разрядное число, включенное в команду.

База -- это содержимое базового регистра процессора. Обычно оно используется для указания на начало некоторого массива.

Индекс -- это содержимое индексного регистра процессора. Обычно оно используется для выбора одного из элементов массива.

Масштаб -- это множитель (он может быть равен 1, 2, 4 или 8), указанный в коде команды, на который перед суммированием с другими компонентами умножается индекс. Он используется для указания размера элемента массива.

Затем специальный блок сегментации вычисляет 32-разрядный линейный адрес, который представляет собой сумму базового адреса сегмента из сегментного регистра с эффективным адресом. Наконец, физический 32-битный адрес памяти образуется путем преобразования линейного адреса блоком страничной переадресации, который осуществляет перевод линейного адреса в физический страницами по 4 Кбайт. В любом случае сегментирование позволяет выделить в памяти один или несколько сегментов для данных и один или несколько сегментов для программ. Переход от одного сегмента к другому сводится всего лишь к изменению содержимого сегментного регистра. Иногда это бывает очень удобно. Но для программиста работать с сегментированной памятью обычно сложнее, чем с непрерывной, несегментированной памятью, так как приходится следить за границами сегментов, за их описанием, переключением и т. д.

Свопинг

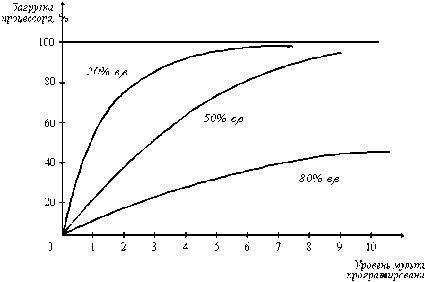

Разновидностью виртуальной памяти является свопинг. На рисунке 8.7 показан график зависимости коэффициента загрузки процессора в зависимости от числа одновременно выполняемых процессов и доли времени, проводимого этими процессами в состоянии ожидания ввода-вывода.

Рис. 8.7 Зависимость загрузки процессора от числа задач и интенсивности ввода-вывода

Из рисунка видно, что для загрузки процессора на 90% достаточно всего трех счетных задач. Однако для того, чтобы обеспечить такую же загрузку интерактивными задачами, выполняющими интенсивный ввод-вывод, потребуются десятки таких задач. Необходимым условием для выполнения задачи является загрузка ее в оперативную память, объем которой ограничен. В этих условиях был предложен метод организации вычислительного процесса, называемый свопингом. В соответствии с этим методом некоторые процессы (обычно находящиеся в состоянии ожидания) временно выгружаются на диск. Планировщик операционной системы не исключает их из своего рассмотрения, и при наступлении условий активизации некоторого процесса, находящегося в области свопинга на диске, этот процесс перемещается в оперативную память. Если свободного места в оперативной памяти не хватает, то выгружается другой процесс. При свопинге, в отличие от рассмотренных ранее методов реализации виртуальной памяти, процесс перемещается между памятью и диском целиком, то есть в течение некоторого времени процесс может полностью отсутствовать в оперативной памяти. Существуют различные алгоритмы выбора процессов на загрузку и выгрузку, а также различные способы выделения оперативной и дисковой памяти загружаемому процессу.

Выводы

Логическая организация памяти необходима для устранения несоответствия между адресным пространством памяти и ее реальным, физическим объемом.

Для того чтобы адресоваться к операндам и командам, не напрягая при этом адресное пространство памяти, существует много способов. Одна из идей в этой области заключается в том, что адрес ячейки памяти помещают в регистр процессора, а в команде содержится ссылка на этот регистр.

Стековая организация памяти применяется при вызове подпрограмм, временном хранении данных.

Основные разновидности логической организации памяти стековая, сегментная, косвенная, свопинг решают задачу создания виртуальной памяти.

Вопросы и задания

Оцените, какой процент адресного пространства вашего компьютера реально заполнен под память.

Какие методы адресации вы знаете?

Что такое виртуальная память?

Что такое свопинг?

В каких режимах может работать IA-32?

Как формируется физический адрес при сегментной адресации?

Как формируется физический адрес при страничной адресации?

Лекция 9. Методы адресации

Пространство памяти предназначено для хранения кодов команд и данных, для доступа к которым имеется богатый выбор методов адресации (около 24). Операнды могут находиться во внутренних регистрах процессора (наиболее удобный и быстрый вариант). Они могут располагаться в системной памяти (самый распространенный вариант). Наконец, они могут находиться в устройствах ввода/вывода (наиболее редкий случай). Определение места положения операндов производится кодом команды. Причем существуют разные методы, с помощью которых код команды может определить, откуда брать входной операнд и куда помещать выходной операнд. Эти методы называются методами адресации. Эффективность выбранных методов адресации во многом определяет эффективность работы всего процессора в целом.

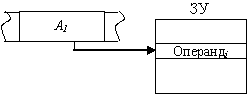

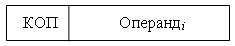

Прямая или абсолютная адресация. Физический адрес операнда содержится в адресной части команды. Формальное обозначение:

Операндi = (Аi),

Где Аi - код, содержащийся в i-м адресном поле команды.

Рис. 9.1 Прямая адресация

Пример: mov al,[2000] - передать операнд, который содержится по адресу 2000h в регистр AL.

Add R1,[1000] - сложить содержимое регистра R1 с содержимым ячейки памяти по адресу 1000h и результат переслать в R1.

Допускается использование прямой адресации при обращении, как к основной, так и к регистровой памяти.

Непосредственная адресация. В команде содержится не адрес операнда, а непосредственно сам операнд.

Операндi= Аi.

Рис. 9.2 Непосредственная адресация

Непосредственная адресация позволяет повысить скорость выполнения операции, так как в этом случае вся команда, включая операнд, считывается из памяти одновременно и на время выполнения команды хранится в процессоре в специальном регистре команд (РК). Однако при использовании непосредственной адресации появляется зависимость кодов команд от данных, что требует изменения программы при каждом изменении непосредственного операнда.

Пример: mov eax,0f0f0f0f0 - загрузить константу 0f0f0f0f0h в регистр eax.

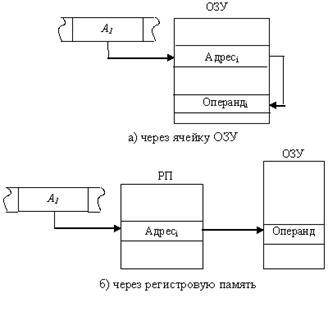

Косвенная (базовая) адресация. Адресная часть команды указывает адрес ячейки памяти (рис. 7.3,а) или номер регистра (рис. 7.3,б), в которых содержится адрес операнда:

Операндi = ((Аi)).

Рис. 9.3 Косвенная адресация

Применение косвенной адресации операнда из оперативной памяти при хранении его адреса в регистровой памяти существенно сокращает длину поля адреса, одновременно сохраняя возможность использовать для указания физического адреса полную разрядность регистра. Недостаток этого способа - необходимо дополнительное время для чтения адреса операнда. Вместе с тем он существенно повышает гибкость программирования. Изменяя содержимое ячейки памяти или регистра, через которые осуществляется адресация, можно, не меняя команды в программе, обрабатывать операнды, хранящиеся по разным адресам. Косвенная адресация не применяется по отношению к операндам, находящимся в регистровой памяти.

Пример: mov al,[ecx] - передать в регистр AL операнд (содержимое) ячейки памяти, адрес которой находится в регистре ECX.

Предоставляемые косвенной адресацией возможности могут быть расширены, если в системе команд ЭВМ предусмотреть определенные арифметические и логические операции над ячейкой памяти или регистром, через которые выполняется адресация, например увеличение или уменьшение их значения на единицу (и не только на 1).

В этом случае речь идет о базовой адресации со смещением.

Пример: mov eax,[eci+4] - передать в EAX операнд, который содержится по адресу ECI со смещением плюс 4.

Иногда, адресация, при которой после каждого обращения по заданному адресу с использованием механизма косвенной адресация, значение адресной ячейки автоматически увеличивается на длину считываемого операнда, называется автоинкрементной. Адресация с автоматическим уменьшением значения адресной ячейки называется автодекрементной.

Регистровая адресация. Предполагается, что операнд находится во внутреннем регистре процессора.

Например: mov eax, cr0 - передать в EAX содержимое CR0 или

Mov ecx, ecx - сбросить регистр ECX.

Индексная адресация (со смещением) - содержимое РОН используется в качестве компоненты эффективного адреса (как правило, работа с массивами).

Пример: sub array [esi],2 - вычесть 2 из элемента массива, на который указывает регистр ESI.

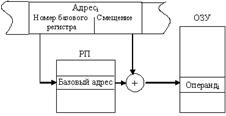

Относительная адресация. Этот способ используется тогда, когда память логически разбивается на блоки, называемые сегментами. В этом случае адрес ячейки памяти содержит две составляющих: адрес начала сегмента (базовый адрес) и смещение адреса операнда в сегменте. Адрес операнда определяется как сумма базового адреса и смещения относительно этой базы:

Операндi = (базаi + смещениеi).

Для задания базового адреса и смещения могут применяться ранее рассмотренные способы адресации. Как правило, базовый адрес находится в одном из регистров регистровой памяти, а смещение может быть задано в самой команде или регистре.

Рассмотрим два примера.

Адресное поле команды состоит из двух частей, в одной указывается номер регистра, хранящего базовое значение адреса (начальный адрес сегмента), а в другом адресном поле задается смещение, определяющее положение ячейки относительно начала сегмента. Именно такой способ представления адреса обычно и называют относительной адресацией.

Рис. 9.4 Относительная адресация

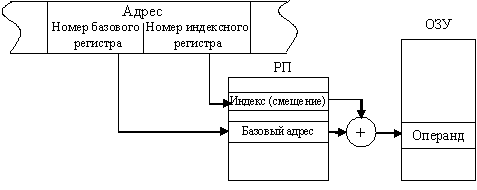

Первая часть адресного поля команды также определяет номер базового регистра, а вторая содержит номер регистра, в котором находится смещение. Такой способ адресации чаще всего называют базово-индексным.

Рис. 9.5 Базово-индексная адресация

Главный недостаток относительной адресации - большое время вычисления физического адреса операнда. Но существенное преимущество этого способа адресации заключается в возможности создания "перемещаемых" программ - программ, которые можно размещать в различных частях памяти без изменения команд программы. То же относится к программам, обрабатывающим по единому алгоритму информацию, расположенную в различных областях ЗУ. В этих случаях достаточно изменить содержимое базового адреса начала команд программы или массива данных, а не модифицировать сами команды. По этой причине относительная адресация облегчает распределение памяти при составлении сложных программ и широко используется при автоматическом распределении памяти в мультипрограммных вычислительных системах.

Лекция 10. Внешняя память компьютера

Введение

У оперативной памяти есть два важных недостатка. Первый -- это цена. Второй недостаток связан с тем, что оперативная память полностью очищается при выключении компьютера, то есть ее нельзя использовать для длительного хранения программ и данных. Поэтому для длительного хранения больших объемов информации нужны другие носители. В качестве таких носителей используют магнитные, оптические, магнитооптические и другие. Скорость обращения к данным у них в тысячи раз меньше, чем у оперативной памяти, но зато меньше цена хранения одного мегабайта, сейчас цена 1 мегабайта порядка одного цента. проблем

В основе действия всех внешних накопительных устройств лежит принцип механического перемещения носителя относительно устройства, выполняющего считывание и запись информации. Чем выше скорость движения, тем быстрее работает устройство. Для достижения сверхвысоких скоростей требуется высочайшая точность изготовления механических частей и герметичное исполнение прибора, исключающее попадание пыли, дыма, влаги и прочего мусора.

Жесткий диск (Hard Disk Drive)

Пока этим требованиям в наибольшей степени удовлетворяют так называемые жесткие диски (HDD -- Hard Disk Drive), хотя не исключено появление в будущем других устройств, обладающих лучшими свойствами. Три основных требования к жесткому диску -- это емкость, быстродействие и минимальные габариты (о надежности мы не говорим, поскольку это, само собой, разумеется). Емкость жестких дисков измеряется в гигабайтах (Гбайт). По состоянию на сегодняшний день емкости жестких дисков уже перевалили за отметку 100 Гбайт.

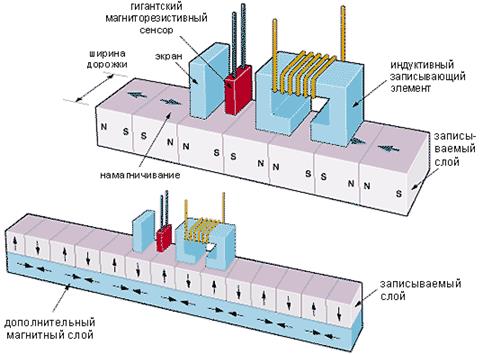

Для создания существующих магнитных дисков применяются технологии, при которых на пластину напыляется один слой магнитного материала - носителя информации, (как на верхнем рисунке).

Традиционный способ записи на магнитную пластину (вверху). При уменьшении размеров единичных ячеек с горизонтальной намагниченностью резко увеличивается вероятность их спонтанного размагничивания. Новый способ, предложенный Fujitsu (внизу). Использование дополнительного подслоя и вертикального намагничивания позволяет достичь в восемь раз большей плотности записи.

Требование емкости напрямую противоречит требованию минимальных габаритов. Это противоречие снимается благодаря непрерывному улучшению технологии изготовления. Сегодня жесткий диск -- это прецизионный прибор, изготовленный с привлечением самых последних достижений технологической науки. Он хрупок, не выносит ударов и требует предельной аккуратности в обращении. По этим причинам жесткий диск стационарно помещается внутри корпуса системного блока. Жесткий диск в совокупности с механическими и электронными устройствами, обеспечивающими его функционирование, называется дисковым накопителем или НМД.

Конструкция жесткого диска

Дисковый накопитель обычно состоит из набора пластин, представляющих собой металлические диски (сегодня большое распространение получили диски из композитных материалов), покрытые магнитным материалом и соединенные между собой при помощи центрального шпинделя. Над каждой поверхностью располагается считывающая головка. При высоких скоростях вращения дисков головки "парят" над их поверхностями на воздушной подушке. Для записи данных используются обе поверхности пластины (керамические, алюминиевые, или из композитных материалов, на которые нанесено специальное магнитное покрытие). В современных дисковых накопителях используется от 4 до 9 пластин. Шпиндель вращается с высокой постоянной скоростью (обычно 3600, 5400 или 7200 оборотов в минуту, но встречаются и более высокие скорости до 15000 об/мин). Каждая пластина содержит набор концентрических записываемых дорожек. Обычно дорожки делятся на блоки данных объемом 512 байт, иногда называемые секторами. Перед данными располагается заголовок (header), состоящий из преамбулы(preamble), которая позволяет головке синхронизироваться перед чтением или записью данных и служебной адресной информацией. После данных идет код с исправлением ошибок (код Хемминга или код Рида-Соломона). Между соседними секторами находится межсекторный интервал. Так что форматированный сектор составляет уже 571 байт. Количество блоков, записываемых на одну дорожку зависит от физических размеров пластины и плотности записи. Как правило, производители указывают размер неформатированного диска (как будто каждая дорожка содержит только данные, но более честно было бы указывать вместимость форматированного диска, когда не учитываются преамбулы, исправляющие коды и межсекторные интервалы. Емкость форматированного диска обычно на 15-20% меньше емкости неформатированного диска.

Данные записываются или считываются с пластин с помощью головок записи/считывания, по одной на каждую поверхность. Линейный двигатель представляет собой электромеханическое устройство, которое позиционирует головку над заданной дорожкой. Обычно головки крепятся на кронштейнах, которые приводятся в движение каретками.

Основные узлы НМД:

Магнитные диски;

Головки записи/считывания;

Двигатель привода дисков;

Механизм привода головок;

Печатная плата с контроллером диска;

Воздушные фильтры, кабели, разъемы и т. д.

Механизм привода головок, с его помощью головки передвигаются от центра диска к его краям и устанавливаются на заданный цилиндр. Различают приводы с шаговым двигателем и сервопривод (с подвижной катушкой), использующий сигнал обратной связи для точного позиционирования над выбранной дорожкой (цилиндром). Сервопривод более дорогое и более точное устройство.

Фильтры, используется два вида фильтров:

Рециркуляции;

Барометрические, необходимые для выравнивания давления внутри устройства с атмосферным.

Накопитель на магнитных дисках (НМД) представляет собой набор пластин, магнитных головок, кареток, линейных двигателей плюс воздухонепроницаемый корпус. Дисковым устройством называется НМД с относящимися к нему электронными схемами (контроллерами). Некоторые контроллеры содержат микропроцессор, производят буферизацию совокупности секторов и кэширование данных, а также устраняют поврежденные секторы.

Основные характеристики НМД:

Тип привода головок;

Способ парковки;

Надежность;

Быстродействие, производительность, стоимость;

Вид интерфейса (IDE, EIDE, SCSI).

Производительность диска является функцией времени обслуживания, которое включает в себя три основных компонента: время доступа, время ожидания и время передачи данных. Время доступа - это время, необходимое для позиционирования головок на соответствующую дорожку, содержащую искомые данные. Оно является функцией затрат на начальные действия по ускорению головки диска (порядка 6 мс), а также функцией числа дорожек, которые необходимо пересечь на пути к искомой дорожке. Характерные средние времена поиска - время, необходимое для перемещения головки между двумя случайно выбранными дорожками, лежат в диапазоне 10-20 мс. Время перехода с дорожки на дорожку меньше 10 мс и обычно составляет 2 мс. Вторым компонентом времени обслуживания является время ожидания. Чтобы искомый сектор повернулся до совмещения с положением головки требуется некоторое время. После этого данные могут быть записаны или считаны. Для современных дисков время полного оборота лежит в диапазоне 8-16 мс, а среднее время ожидания составляет 4-8 мс.

Последним компонентом является время передачи данных, т. е. время, необходимое для физической передачи байтов. Время передачи данных является функцией от числа передаваемых байтов (размера блока), скорости вращения, плотности записи на дорожке и скорости электроники. Типичная скорость считывания информации равна 1-15 Мбайт/с.

Пример:

HAD компании Seagate Technology, объем - 9 Гбайт, среднее время доступа - 8 мс, скорость - 7200 об/мин, интерфейс Fast SCSI -2, скорость считывания - 13 Мбайт/сек.

Способы кодирования данных

В современных системах для процесса записи/считывания используется гигантский магнито-резистивный эффект (GMR - Giant magnetic Resistance), который позволяет реализовать достаточно высокую плотность записи. Сам процесс записи и считывания основан на физических явлениях, описанных еще Фарадеем. Проиллюстрируем эти процессы с помощью рисунка 8.1.

Поскольку количество зон смены знака (их называют битовые ячейки) ограничено возможностями технологии применяются различные способы кодирования, позволяющие, как бы, "втиснуть" как можно больше битов данных в отведенное количество зон.

Различают:

Частотная модуляция - FM (одинарная плотность - Single density);

Модифицированный частотный сигнал - MFM (двойная плотность - Double density);

Кодирование с ограниченной длиной поля записи - RLL (самый популярный сегодня).

Интерфейсы НМД

В состав компьютеров часто входят специальные устройства, называемые дисковыми контроллерами. К каждому дисковому контроллеру может подключаться несколько дисковых накопителей. Между дисковым контроллером и основной памятью может быть целая иерархия контроллеров и магистралей данных, сложность которой определяется главным образом стоимостью компьютера. Поскольку время передачи часто составляет очень небольшую часть общего времени доступа к диску, контроллер в высокопроизводительной системе разъединяет магистрали данных от диска на время позиционирования так, что другие диски, подсоединенные к контроллеру, могут передавать свои данные в основную память. Поэтому время доступа к диску может увеличиваться на время, связанное с накладными расходами контроллера на организацию операции ввода/вывода.

Необходимо отметить, что в последнее время все большее распространение получил интерфейс SCSI. Он не только более производителен, но и поддерживает до 16 устройств, что очень важно для файл-серверов и серверов сети.

Структура хранения информации на жестком диске

Компьютеру важно не просто записать информацию на диск, а так записать, ее, чтобы потом найти, причем быстро и безошибочно. Поэтому на жестком диске создается специальная структура для хранения данных. Операция создания такой структуры называется форматированием диска. После форматирования каждый файл, записанный на диск, может иметь собственный адрес, выраженный в числовой форме.

Несмотря на то, что физически жесткий диск состоит из п дисков и имеет 2п поверхностей, для изучения его структуры нам достаточно рассмотреть только одну поверхность. Эта поверхность разбивается на концентрические дорожки. В зависимости от конструкции диска таких дорожек может быть больше или меньше, и каждая дорожка имей свой уникальный номер.

Если мы теперь вновь вспомним, что реальный жесткий диск имеет много поверхностей, то у нас появится новый термин -- цилиндр. Дорожки с одинаковыми номерами, но принадлежащие разным поверхностям, образуют один цилиндр. Каждый цилиндр имеет номер, совпадающий с номером входящих в него дорожек.

Дорожки, в свою очередь, разбиваются на секторы. Длина каждого сектора равна 512 байтам данных. Таким образом, сектор -- наименьший элемент структуры жесткого диска. Для того чтобы записать, а затем затребовать информацию, необходимо задать адрес, состоящий из трех чисел: номера цилиндра, номера поверхности (номера головки) и номера сектора. Этот метод называется CHS (Cylinder Head Sector). Современным развитием этого метода является механизм трансляции линейных адресов и линейной адресации LBA (Logical Block Adressing), связанный однозначно с CHS.

Таблица размещения файлов

Файлы в канцелярском понимании -- это "дела", с обычными человеческими именами, пылящиеся в таком месте, куда месяцами не ступает нога человека, но установить это место всегда можно по номеру "дела", если заглянуть в амбарную книгу, называемую реестром.

Роль такого "реестра" на жестком диске выполняет специальная таблица, которая называется FAT-таблицей File Allocation Table (по-русски: таблица размещения файлов). Она находится на служебной дорожке жесткого диска и должна именовать, сохранять и производить поиск данных. Физическое повреждение секторов, в которых записана эта таблица, равносильно краху всей информации, хранящейся на жестком диске, поэтому эта таблица всегда продублирована, и операционная система компьютера бережно следит за тем, чтобы информация в разных экземплярах таблицы строго совпадала. Для ОС W.95/98 это были FAT 16 и FAT 32. В этих случаях размер кластера определялся объемом HDD. Однако FAT 32 поддерживал только 32 Гбайт (W.95) при размере кластера 16 Кбайт. Это заставило разработчиков перейти на NTFS начиная с ОС Windows 2000 (для ПК), хотя эта система успешно работала и с Win. NT. Основными преимуществами NTFS является умение управлять дисками с объемом несколько терабайт, исправлять ошибки после сбоев и защищать систему от несанкционированного доступа. Вместе с тем ограниченное количество логических дисков, потери при перезагрузке при изменении размеров кластера вынудили разработчиков к дальнейшему совершенствованию системы. Итак, улучшенная NTFS называется WinFS для ОС Windows Longhorn. Теперь структура каталогов будет давать представление не только о месте хранения файлов, но и определять его предысторию.

Кластер

Хотя острота проблемы с кластеризацией пропала, особенно с внедрением NTFS мы должны понимать откуда она возникла.

Сейчас мы узнаем, откуда эти кластеры берутся. Мы работаем с файлами, имеющими имена, записанные символами (обычными человеческими буквами). Компьютер переводит эти имена в числовые адреса секторов с помощью таблицы размещения файлов. Этим занимается неоднократно упомянутая нами операционная система. Конечно, каждая система делает это по-разному, но до последнего времени все операционные системы, работающие на компьютерах платформы IBM PC, выражали адрес шестнадцатиразрядным числом, поскольку в таблицах размещения файлов на запись адреса каждого сектора зарезервировано 2 байта.

Имея 16 двоичных разрядов, можно задать 65536 разных адресов (216). При такой системе на диск можно записать 65536 различных файлов, и у каждого будет свой уникальный адрес. В те годы, когда размеры жестких дисков не превышали 32 мегабайта, это было очень неплохо. Сегодня средний размер жесткого диска вырос в сто раз, а количество уникальных адресов для записи файлов осталось тем же, каким было. Предельный размер диска, к какому вообще в принципе может адресоваться операционная система, работающая с 16-разрядной FAT-таблицей, сегодня составляет 2 Гбайт. А если мы поделим этот размер на 65536 адресов, то получим, что минимально адресуемое пространство жесткого диска составляет 32 Кбайт. Эта единица и называется кластером.

Поскольку кластер -- это минимальное адресуемое дисковое пространство, значит, ни один файл не может занимать меньше места, чем составляет кластер. На больших дисках файл, имеющий размер 1 байт, займет все 32 Кбайт. То же произойдет и с файлом длиной 2 байта и т. д. Если файл имеет размер 32,1 Кбайт, он займет два кластера, то есть все 64 Кбайт. Даже для FAT 32 при размере диска 32 Гбайт величина кластера все еще остается большой - 16 Кбайт. Потери от кластеризации жестких дисков составляют огромную величину, в отдельных случаях достигающую 40% их объема.

Методы борьбы с кластеризацией

Как уже упоминалось, логическая структура ЖД довольно сложна: дорожки, цилиндры, сектора, которые группируются в кластеры. Реализуется логическая структура на самом диске с помощью технологической операции - форматирование.

Форматирование ЖД выполняется в три этапа:

Форматирование низкого уровня (физическое);

Разбиение диска на разделы;

Форматирование высокого уровня (логическое).

Форматирование низкого уровня - дорожки диска разбиваются на секторы (512 байт данных каждый), приписываются заголовок - преамбула (Header или preamble), концевик, в котором содержится код проверки (Trailer), т. е. добавляется служебная информация, полная емкость сектора становится равной 571 байт.

Разбиение диска на разделы - проводится в том случае, когда на одном ПК предполагается использовать несколько ОС.

Форматирование высокого уровня - операционная система создает структуры для работы с файлами и данными, собственно ФВУ не столько форматирование, сколько создание оглавления диска и таблицы размещения файлов FAT (File Allocation Table).

Самый простой метод борьбы с кластеризацией -- разбиение жесткого диска на разделы (логические диски). Эту операцию производят перед логическим форматированием диска. Для разбиения жесткого диска на разделы применяют программу FDISK. EXE для FAT, которая является приложением MS-DOS, но поставляется и в составе Windows 95, и в составе Windows 98 или Partition Magic для NTFS (W.200 и W. XP). При разбиении жесткого диска на несколько логических дисков каждый вновь образующийся диск имеет собственную структуру и свою таблицу размещения файлов, поэтому чем меньше размеры полученных логических дисков, тем меньше и размеры их кластеров.

Начиная с Windows NT быстро прогрессирует NTFS (NT File System). В этой файловой системе длина имени файла может быть до 255 символов. Имена написаны в коде Unicode, благодаря чему люди в разных странах, где не используется латинский алфавит, могут писать имена файлов на их родном языке. Самое главное в этой системе размер кластера может быть задан вручную, независимо от объема диска.

Дефрагментация дисков - операционная система не всегда располагает информацию файлов и папок в одном непрерывном пространстве. Фрагменты данных могут находится в различных кластерах ЖД, более того, при удалении файлов освобождающееся дисковое пространство становится фрагментированным. Это существенно влияет на производительность файловой системы. Для решения этой проблемы применяется Disk Defragmenter (Дефрагментация диска). В процессе дефрагментации кластеры диска организуются таким образом, чтобы файлы, папки и свободное пространство по возможности располагались равномерно. В результате значительно повышается производительность файловой системы.

Магнито-оптические диски

Другим направлением развития систем хранения информации являются магнитооптические диски. Запись на магнитооптические диски (МО-диски) выполняется при взаимодействии лазера и магнитной головки. Луч лазера разогревает до точки Кюри (температуры потери материалом магнитных свойств) микроскопическую область записывающего слоя, которая при выходе из зоны действия лазера остывает, фиксируя магнитное поле, наведенное магнитной головкой. В результате данные, записанные на диск, не боятся сильных магнитных полей и колебаний температуры. Все функциональные свойства дисков сохраняются в диапазоне температур от -20 до +50 градусов Цельсия. В то время, как вектор намагничивания при традиционной записи ориентирован в плоскости его поверхности диска, с помощью магнито-оптических технологий удается придать вектору вертикальную ориентацию, что значительно ослабляет взаимодействие доменов, а значит чувствительность к внешним полям и высоким температурам.

Конструктивно магнитооптический диск состоит из толстой стеклянной подложки, на которую наносится светоотражающая алюминиевая пленка и ферромагнитный сплав -- носитель информации, покрытый сверху защитным слоем прозрачного пластика. У таких дисков диаметром 3,5 дюйма информационная емкость одной стороны достигает 128-230 Мбайт, при диаметре 5,25 дюйма -- 600 Мбайт, с двух сторон -- 1,3 Гбайт. Дисководы могут быть как встроенными, так и внешними. МО-диски уступают обычным жестким магнитным дискам лишь по времени доступа к данным. Предельное достигнутое МО-дисками время доступа составляет 19 мс. Магнитооптический принцип записи требует предварительного стирания данных перед записью, и соответственно, дополнительного оборота МО-диска. Однако завершенные недавно исследования в SONY и IBM показали, что это ограничение можно устранить, а плотность записи на МО-дисках можно увеличить в несколько раз используя голубой лазер. Во всех других отношениях МО-диски превосходят жесткие магнитные диски.

В магнитооптическом дисководе используются сменные диски, что обеспечивает практически неограниченную емкость. Стоимость хранения единицы данных на МО-дисках в несколько раз меньше стоимости хранения того же объема данных на жестких магнитных дисках.

Сегодня на рынке МО-дисков предлагается более 150 моделей различных фирм. Одно из лидирующих положений на этом рынке занимает компания Pinnacle Micro Inc. Для примера, ее дисковод Sierra 1.3 Гбайт обеспечивает среднее время доступа 19 мс и среднее время наработки на отказ 80000 часов. Для серверов локальных сетей и рабочих станций компания Pinnacle Micro предлагает целый спектр многодисковых систем емкостью 20, 40, 120, 186 Гбайт и даже 4 Тбайт. Для систем высокой готовности Pinnacle Micro выпускает дисковый массив Array Optical Disk System, который обеспечивает эффективное время доступа к данным не более 11 мс при скорости передачи данных до 10 Мбайт/с.

Дисковые массивы и уровни RAID

Одним из способов повышения производительности ввода/вывода является использование параллелизма путем объединения нескольких физических дисков в матрицу (группу) с организацией их работы аналогично одному логическому диску. К сожалению, надежность матрицы любых устройств падает при увеличении числа устройств.

Для достижения повышенного уровня отказоустойчивости приходится жертвовать пропускной способностью ввода/вывода или емкостью памяти. Необходимо использовать дополнительные диски, содержащие избыточную информацию, позволяющую восстановить исходные данные при отказе диска. Отсюда получают акроним для избыточных матриц недорогих дисков RAID (redundant array of inexpensive disks). Существует несколько способов объединения дисков RAID. Каждый уровень представляет свой компромисс между пропускной способностью ввода/вывода и емкостью диска, предназначенной для хранения избыточной информации.

Когда какой-либо диск отказывает, предполагается, что в течение короткого интервала времени он будет заменен и информация будет восстановлена на новом диске с использованием избыточной информации. Это время называется средним временем восстановления (mean time to repair - MTTR). Этот показатель можно уменьшить, если в систему входят дополнительные диски в качестве "горячего резерва": при отказе диска резервный диск подключается аппаратно-программными средствами. Периодически оператор вручную заменяет все отказавшие диски. Четыре основных этапа этого процесса состоят в следующем:

Определение отказавшего диска,

Устранение отказа без останова обработки;

Восстановление потерянных данных на резервном диске;

Периодическая замена отказавших дисков на новые.

RAID1: Зеркальные диски.

Зеркальные диски представляют традиционный способ повышения надежности магнитных дисков. Это наиболее дорогостоящий из рассматриваемых способов, так как все диски дублируются и при каждой записи информация записывается также и на проверочный диск. Таким образом, приходится идти на некоторые жертвы в пропускной способности ввода/вывода и емкости памяти ради получения более высокой надежности. Зеркальные диски широко применяются многими фирмами. В частности компания Tandem Computers применяет зеркальные диски, а также дублирует контроллеры и магистрали ввода/вывода с целью повышения отказоустойчивости. Эта версия зеркальных дисков поддерживает параллельное считывание.

Дублирование всех дисков может означать удвоение стоимости всей системы или, иначе, использование лишь 50% емкости диска для хранения данных. Повышение емкости, на которое приходится идти, составляет 100%. Такая низкая экономичность привела к появлению следующего уровня RAID.

RAID 2: матрица с поразрядным расслоением

Один из путей достижения надежности при снижении потерь емкости памяти может быть подсказан организацией основной памяти, в которой для исправления одиночных и обнаружения двойных ошибок используются избыточные контрольные разряды. Такое решение можно повторить путем поразрядного расслоения данных и записи их на диски группы, дополненной достаточным количеством контрольных дисков для обнаружения и исправления одиночных ошибок. Один диск контроля четности позволяет обнаружить одиночную ошибку, но для ее исправления требуется больше дисков.

При записи больших массивов данных системы уровня 2 имеют такую же производительность, что и системы уровня 1, хотя в них используется меньше контрольных дисков и, таким образом, по этому показателю они превосходят системы уровня 1. При передаче небольших порций данных производительность теряется, так как требуется записать либо считать группу целиком, независимо от конкретных потребностей.

RAID 3: аппаратное обнаружение ошибок и четность

Большинство контрольных дисков, используемых в RAID уровня 2, нужны для определения положения неисправного разряда. Эти диски становятся полностью избыточными, так как большинство контроллеров в состоянии определить, когда диск отказал при помощи специальных сигналов, поддерживаемых дисковым интерфейсом, либо при помощи дополнительного кодирования информации, записанной на диск и используемой для исправления случайных сбоев. По существу, если контроллер может определить положение ошибочного разряда, то для восстановления данных требуется лишь один бит четности. Уменьшение числа контрольных дисков до одного на группу снижает избыточность емкости до вполне разумных размеров. Часто количество дисков в группе равно 5 (4 диска данных плюс 1 контрольный). Подобные устройства выпускаются, например, фирмами Maxtor и Micropolis. Каждое из таких устройств воспринимается машиной как отдельный логический диск с учетверенной пропускной способностью, учетверенной емкостью и значительно более высокой надежностью.

RAID 4: внутригрупповой параллелизм

RAID уровня 4 повышает производительность передачи небольших объемов данных за счет параллелизма, давая возможность выполнять более одного обращения по вводу/выводу к группе в единицу времени. Логические блоки передачи в данном случае не распределяются между отдельными дисками, вместо этого каждый индивидуальный блок попадает на отдельный диск.

Достоинство поразрядного расслоения состоит в простоте вычисления кода Хэмминга, что необходимо для обнаружения и исправления ошибок в системах уровня 2. В RAID уровня 3 обнаружение ошибок диска с точностью до сектора осуществляется дисковым контроллером. Следовательно, если записывать отдельный блок передачи в отдельный сектор, то можно обнаружить ошибки отдельного считывания без доступа к дополнительным дискам. Главное отличие между системами уровня 3 и 4 состоит в том, что в последних расслоение выполняется на уровне сектора, а не на уровне битов или байтов.

В системах уровня 4 для записи небольших массивов данных используются два диска, которые выполняют четыре выборки (чтение данных плюс четности, запись данных плюс четности). Производительность групповых операций записи и считывания остается прежней, но при небольших (на один диск) записях и считываниях производительность существенно улучшается. К сожалению, улучшение производительности оказывается недостаточной для того, чтобы этот метод мог занять место системы уровня 1.

RAID 5: четность вращения для распараллеливания записей

RAID уровня 4 позволяли добиться параллелизма при считывании отдельных дисков, но запись по-прежнему ограничена возможностью выполнения одной операции на группу, так как при каждой операции должны выполняться запись и чтение контрольного диска. Система уровня 5 улучшает возможности системы уровня 4 посредством распределения контрольной информации между всеми дисками группы.

Это небольшое изменение оказывает огромное влияние на производительность записи небольших массивов информации. Если операции записи могут быть спланированы так, чтобы обращаться за данными и соответствующими им блоками четности к разным дискам, появляется возможность параллельного выполнения N/2 записей, где N - число дисков в группе. Данная организация имеет одинаково высокую производительность при записи и при считывании как небольших, так и больших объемов информации, что делает ее наиболее привлекательной в случаях смешанных применений.

RAID 6: Двумерная четность для обеспечения большей надежности

Этот пункт можно рассмотреть в контексте соотношения отказоустойчивость/пропускная способность. RAID 5 предлагают, по существу, лишь одно измерение дисковой матрицы, вторым измерением которой являются секторы. Теперь рассмотрим объединение дисков в двумерный массив таким образом, чтобы секторы являлись третьим измерением. Мы можем иметь контроль четности по строкам, как в системах уровня 5, а также по столбцам, которые, в свою очередь. могут расслаиваться для обеспечения возможности параллельной записи. При такой организации можно преодолеть любые отказы двух дисков и многие отказы трех дисков. Однако при выполнении логической записи реально происходит шесть обращений к диску: за старыми данными, за четностью по строкам и по столбцам, а также для записи новых данных и новых значений четности. Для некоторых применений с очень высокими требованиями к отказоустойчивости такая избыточность может оказаться приемлемой, однако для традиционных суперкомпьютеров и для обработки транзакций данный метод не подойдет.

Лазерные компакт-диски CD - ROM

Для переноса больших объемов данных используют лазерные компакт-диски, получившие обозначение CD-ROM (Compact Disc Read Only Memory). В силу большой емкости (один диск может содержать до 650 Мбайт данных) эти носители широко используются для распространения мультимедийной информации, содержащей большие объемы графики, звука и видео. Они также не имеют конкурентов по параметру стоимости хранения мегабайта информации.

Сегодня диски CD-ROM являются основным типом носителя для распространения программного обеспечения. Если компьютер не имеет дисковода CD-ROM, установка нового программного обеспечения превращается в серьезную проблему.

Основным техническим требованием к дисководам CD-ROM является скорость доступа к данным и скорость их считывания. Этот параметр измеряется в кратных единицах. Так, например, 2-скоростные дисководы обеспечивают скорость считывания 300 Кбит в секунду. Соответственно, 4-скоростные дисководы обеспечивают скорость 600 Кбит в секунду и т. д.

Производительность дисковода CD-ROM нам чаще всего важна не сама по себе, а в сравнении с производительностью жесткого диска. Современные 24- и 32-скоростные дисководы CD-ROM по параметру скорости считывания данных намного превосходят жесткие диски, но могут уступать им во времени доступа к данным.

Лазерные компакт-диски не боятся магнитных полей и менее критичны к пыли и влаге, чем магнитные дискеты. В то же время, в большинстве случаев они не защищены пластиковым корпусом, как магнитные дискеты, и при неакуратном обращении могут получать механические повреждения: царапины, трещины, сколы и т. п. В качестве интерфейса применяются SCSI/ASPI - самый подходящий, но дорогой, иногда рекомендуется - IDI/ATAPI.

CD-R

В отличие от CD-ROM могут не только читать диски, но и записывать их. Могут устанавливаться в компьютер вместо CD-ROM. Запись на диски CD-R осуществляется благодаря наличию на нем особо светочувствительного слоя, выгорающего под воздействием высокотемпературного лазерного луча. То есть перед нами нечто похожее на обычную фотографию. Правда, считывает CD-R по нынешним временам не слишком быстро - со скоростью 8-скоростного CD-ROM (8 x 150 = 1200 кб/c = 1,17 Мб/c), но ведь чтение - не главная его функция. Главная - запись. Писать CD-R может в 2-х режимах - односессионном (когда весь диск записывается в один прием) и многосессионном. CD-R - идеален для хранения всевозможных архивов (изображений, звуков, да и просто программ, загромождающих место на вашем жестком диске). Можно сделать копию содержимого всего жесткого диска (на всякий случай). И, конечно же, копировать аудио-, видеодиски и программы.

CD-RW

Новый стандарт перезаписываемых CD-ROM. Внешне диски не отличаются от обычных CD-R, объем - тот же - 640 Мб. Но технология записи CD-R и CD-RW разная.

На дисках CD-RW также имеются поглощающие и отражающие свет участки. Однако это не бугорки или ямки, как в дисководах CD-ROM и CD-R. Диск CD-RW представляет из себя как бы слоеный пирог, где на металлической основе покоится рабочий, активный слой. Он состоит из специального материала, который под воздействием лазерного луча изменяет свое состояние. Находясь в кристаллическом состоянии, одни участки слоя рассеивают свет, а другие - аморфные - пропускают его через себя на отражающую металлическую подложку.

Достоинства:

На диск можно записывать информацию и читать ее;

Дисковод CD-RW использует как диски собственного формата, так и с диски CD-ROM и CD-R. Последние он не только читает, но и пишет, причем в любом - односессионном или многосессионном формате.

Недостатки:

Перезаписываемые диски CD-RW могут читать не все современные дисководы CD-ROM - только последние модели, соответствующие стандарту Multiread. И даже если вы запишите на CD-RW музыкальный диск, его не прочтет ни один чисто музыкальный компакт-проигрыватель.

Высокая цена: цена диска в 2 - 2,5 раза выше, чем у CD-R.

Низкая скорость: запись дисков - максимум на учетверенной скорости, а чтение - со скоростью 6х и 8х.

DVD

В свое время к 2000 году, по обещаниям разработчиков, видеокассеты, компакт-диски и другие носители информации должны были прекратить свое существование. Их должны были заменить Единые и Универсальные - DVD.

Сначала DVD расшифровывался так - Digital Video Disk - цифровой видеодиск нового поколения. Но позднее консорциум DVD отказался от этой расшифровки. Впервые слово DVD прозвучало в мире 8 декабря 1995 года. DVD может быть односторонним и двухсторонним, однослойным и многослойным. Но фирмы, входящие в консорциум так до сих пор решение и не приняли. Поэтому пока остановились на односторонних и однослойных.

По внешнему виду и способу записи DVD не очень отличаются от привычных CD-ROM. Но однослойный и односторонний DVD имеет емкость 4,7 Гбайт (в 8 раз больше объема CD-ROM). Объем двухстороннего и многослойного DVD может достигать 17 Гбайт. На одном DVD можно уместить видеофильм на 140 минут с пятью альтернативными звуковыми дорожками на разных языках и четырьмя каналами субтитров. Сравнительно недавно появились первые записывающие дисководы DVD-R, а в дальнейшем - перезаписывающие дисководы DVD-RW (DVD-RAM), работающие с односторонними однослойными дисками емкостью 4,7 Гбайт (или 5,2 Гбайт - в зависимости от производителя). В дальнейшем появились DVD-RW, работающие с многослойными дисками объемом до и более 10 Гбайт.

Можно было бы продолжить обзор устройств внешней памяти, однако как бы мы не поспешали прогресс в этой области обогнать невозможно. С каждой минутой появляются не только новые устройства, но и совершенно новые принципы хранения информации.

Выводы

Основная функция всех видов внешней памяти ЭВМ состоит в том, чтобы сохранять информацию для повторного использования, а также для использования виртуального увеличения объема памяти.

Данные на внешних носителях недоступны человеку без помощи компьютера.

Информация на носителях внешней памяти хранится в виде отдельных блоков - секторов. Сектор является неделимой единицей информации, т. е. может быть прочитан только целиком.

В обмене данными между внешней памятью и внутренней существенную роль играют контроллеры (интерфейсы), которые обслуживают диск.

В любой момент времени процессор работает только с ОП, в которую она предварительно заносится из ВП.

Все виды памяти связаны между собой, образуя общую иерархию.

Вопросы и задания

Что такое кластер? Перечислите методы борьбы с кластеризацией.

Дайте развернутую характеристику FAT 32.

В чем состоит различие между физическим и логическим форматированием7

Как и в каких случаях выполняется дефрагментация ЖД?

В чем заключается смысл и предназначение RAID-массивов?

Лекция 11. Основные принципы построения систем ввода/вывода

Функционирование любой вычислительной системы обычно сводится к выполнению двух видов работы: обработке информации и операций по осуществлению ее ввода-вывода. Содержание понятий "обработка информации" и "операции ввода-вывода" зависит от того, с какой точки зрения мы смотрим на них. С точки зрения программиста, под "обработкой информации" понимается выполнение команд процессора над данными, лежащими в памяти независимо от уровня иерархии - в регистрах, кэше, оперативной или вторичной памяти. Под "операциями ввода-вывода" программист понимает обмен данными между памятью и устройствами, внешними по отношению к памяти и процессору, такими как магнитные ленты, диски, монитор, клавиатура, таймер. С точки зрения операционной системы "обработкой информации" являются только операции, совершаемые процессором над данными, находящимися в памяти на уровне иерархии не ниже, чем оперативная память. Все остальное относится к "операциям ввода-вывода". Чтобы выполнять операции над данными, временно расположенными во вторичной памяти, операционная система, сначала производит их подкачку в оперативную память, и лишь затем процессор совершает необходимые действия.

Данная лекция будет посвящена второму виду работы вычислительной системы - операциям ввода-вывода. Мы разберем, что происходит в компьютере при выполнении операций ввода-вывода, и как операционная система управляет их выполнением. При этом для простоты будем считать, что объем оперативной памяти в вычислительной системе достаточно большой, т. е. все процессы полностью располагаются в оперативной памяти, и поэтому понятие "операция ввода-вывода" с точки зрения операционной системы и с точки зрения пользователя означает одно и то же. Такое предположение не снижает общности нашего рассмотрения, так как подкачка информации из вторичной памяти в оперативную память и обратно обычно строится по тому же принципу, что и все операции ввода-вывода.

Прежде чем говорить о работе операционной системы при осуществлении операций ввода-вывода, нам придется понять, как осуществляется передача информации между оперативной памятью и внешним устройством и почему для подключения к вычислительной системе новых устройств ее не требуется перепроектировать.

Физические принципы организации ввода-вывода

Существует много разнообразных устройств, которые могут взаимодействовать с процессором и памятью: таймер, жесткие диски, клавиатура, дисплеи, мышь, модемы и т. д., вплоть до устройств отображения и ввода информации в авиационно-космических тренажерах. Часть этих устройств может быть встроена внутрь корпуса компьютера, часть вынесена за его пределы и общаться с компьютером через различные линии связи: кабельные, оптоволоконные, радиорелейные, спутниковые и т. д. Конкретный набор устройств и способы их подключения определяются целями функционирования вычислительной системы, желаниями и финансовыми возможностями пользователя. Несмотря на все многообразие устройств, управление их работой и обмен информацией с ними строятся на относительно небольшом наборе принципов, которые мы постараемся разобрать в этом разделе.

Любая ЭВМ представляет собой сложную систему, включающую в себя большое количество различных устройств. Связь устройств ЭВМ между собой осуществляется с помощью сопряжения, которые в вычислительной технике называются интерфейсами.

Интерфейс

Интерфейс - это совокупность программных и аппаратных средств, предназначенных для передачи информации между компонентами ЭВМ и включающих в себя электронные схемы, линии, шины и сигналы адресов, данных и управления, алгоритмы передачи сигналов и правила интерпретации сигналов устройствами.

Интерфейсы характеризуются следующими параметрами:

Пропускная способность - количество информации, которая может быть передана через интерфейс в единицу времени;

Максимальная частота передачи информационных сигналов через интерфейс;

Максимально допустимое расстояние между соединяемыми устройствами;

Общее число проводов (линий) в интерфейсе;

Информационная ширина интерфейса - число бит или байт данных, передаваемых параллельно через интерфейс.

К динамическим параметрам интерфейса относится время передачи отдельного слова и блока данных с учетом продолжительности процедур подготовки и завершения передачи. Разработка систем ввода-вывода требует решения целого ряда проблем, среди которых выделим следующие:

Необходимо обеспечить возможность реализации ЭВМ с переменным составом оборудования, в первую очередь, с различным набором устройств ввода-вывода, с тем, чтобы пользователь мог выбирать конфигурацию машины в соответствии с ее назначением, легко добавлять новые устройства и отключать те, в использовании которых он не нуждается;

Для эффективного и высокопроизводительного использования оборудования компьютера следует реализовать параллельную во времени работу процессора над вычислительной частью программы и выполнение периферийными устройствами процедур ввода-вывода;

Необходимо упростить для пользователя и стандартизовать программирование операций ввода-вывода, обеспечить независимость программирования ввода-вывода от особенностей того или иного периферийного устройства;

В ЭВМ должно быть обеспечено автоматическое распознавание и реакция процессора на многообразие ситуаций, возникающих в УВВ (готовность устройства, отсутствие носителя, различные нарушения нормальной работы и др.).

Магистрально-модульный способ построения ЭВМ

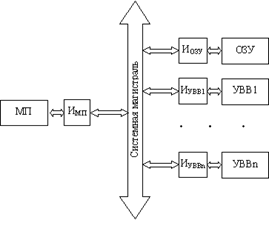

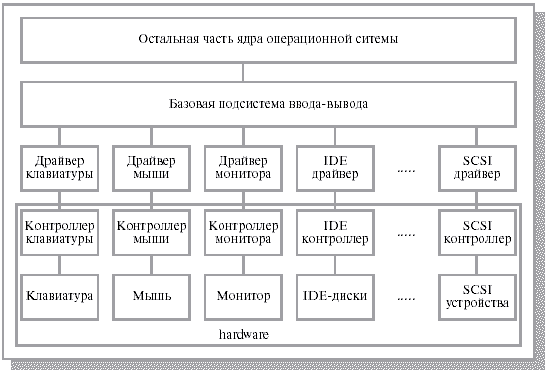

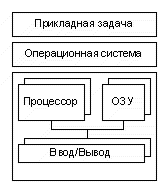

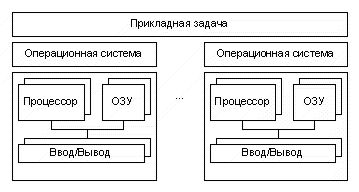

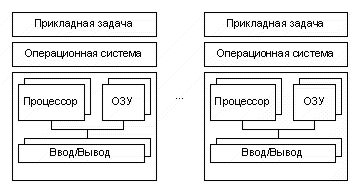

Главным направлением решения указанных проблем является магистрально-модульный способ построения ЭВМ (рис.9.1) все устройства, составляющие компьютер, включая и микропроцессор, организуются в виде модулей, которые соединяются между собой общей магистралью. Обмен информацией по магистрали удовлетворяет требованиям некоторого общего интерфейса, установленного для магистрали данного типа. Каждый модуль подключается к магистрали посредством специальных интерфейсных схем (Иi).

Рис. 11.1 Магистрально-модульный принцип построения ЭВМ

На интерфейсные схемы модулей возлагаются следующие задачи:

Обеспечение функциональной и электрической совместимости сигналов и протоколов обмена модуля и системной магистрали;

Преобразование внутреннего формата данных модуля в формат данных системной магистрали и обратно;

Обеспечение восприятия единых команд обмена информацией и преобразование их в последовательность внутренних управляющих сигналов.

Эти интерфейсные схемы могут быть достаточно сложными и по своим возможностям соответствовать универсальным микропроцессорам. Такие схемы принято называть контроллерами. Контроллеры обладают высокой степенью автономности, что позволяет обеспечить параллельную во времени работу периферийных устройств и выполнение программы обработки данных микропроцессором. Недостатком магистрально-модульного способа организации ЭВМ является невозможность одновременного взаимодействия более двух модулей, что ставит ограничение на производительность компьютера. Поэтому этот способ, в основном, используется в ЭВМ, к характеристикам которых не предъявляется очень высоких требований, например в персональных ЭВМ.

В простейшем случае процессор, память и многочисленные внешние устройства связаны большим количеством электрических соединений - линий, которые в совокупности принято называть локальной магистралью компьютера. Внутри локальной магистрали линии, служащие для передачи сходных сигналов и предназначенные для выполнения сходных функций, принято группировать в шины. При этом понятие шины включает в себя не только набор проводников, но и набор жестко заданных протоколов, определяющий перечень сообщений, который может быть передан с помощью электрических сигналов по этим проводникам. В современных компьютерах выделяют как минимум три шины:

Шину данных, состоящую из линий данных и служащую для передачи информации между процессором и памятью, процессором и устройствами ввода-вывода, памятью и внешними устройствами;

Адресную шину, состоящую из линий адреса и служащую для задания адреса ячейки памяти или указания устройства ввода-вывода, участвующих в обмене информацией;

Шину управления, состоящую из линий управления локальной магистралью и линий ее состояния, определяющих поведение локальной магистрали. В некоторых архитектурных решениях линии состояния выносятся из этой шины в отдельную шину состояния.

Количество линий, входящих в состав шины, принято называть разрядностью (шириной) этой шины. Ширина адресной шины, например, определяет максимальный размер оперативной памяти, которая может быть установлена в вычислительной системе. Ширина шины данных определяет максимальный объем информации, которая за один раз может быть получена или передана по этой шине.

Операции обмена информацией осуществляются при одновременном участии всех шин. Рассмотрим, к примеру, действия, которые должны быть выполнены для передачи информации из процессора в память. В простейшем случае необходимо выполнить три действия.